### CS6235 - Analysis of Parallel Programs Introduction

### V. Krishna Nandivada

IIT Madras

### What, When and Why of Program Analysis

### What:

• A process of automatic analysis of computer programs regarding different program properties.

### • How?

• Analyze the program with or without executing!

### Why? Study?

- Give guarantees about the correctness of program optimization, effectiveness of program optimization, program safety, and so on.

- Used by compilers, debuggers, verifiers, IDEs, profilers.

- A programming language is an artificial language designed to communicate instructions to a machine, particularly a computer.

- Handy, if you care about the programs you write!

### Academic Formalities

- Written assignment = 1 x 10 marks.

- Programming assignments = 3 x 10 marks,

- Project/Paper-reading = 10 marks.

- Quiz 1 = 10 marks, Quiz 2 = 10 marks, Final = 30 marks.

- Extra marks

- During the lecture time individuals can get additional 5 marks.

- How? Ask a <u>good</u> question, answer a <u>chosen</u> question, make a good point! Take 0.5 marks each. Max one mark per day per person.

- Attendance requirement as per institute norms. Non compliance will lead to 'W' grade.

- Proxy attendance is not a help; actually a disservice.

- <u>Plagiarism</u> A good word to know. A bad act to own.

- Will be automatically referred to the institute welfare and disciplinary committee.

CS6235 - Jan 2023

### Contact (Anytime) :

Instructor: Krishna, Email: nvk@iitm.ac.in, Office: BSB 352. TA : Ramya K (cs19d751@smail), Omkar D (cs21s042@smail)

V.Krishna Nandivada (IIT Madras)

2/234

### Flavors of Program Analyses

You have a goal? I have an analysis.

| 1.  | Constant Replacement              | Constant propagation         |

|-----|-----------------------------------|------------------------------|

| 2.  | Method Inlining                   | Points-to analysis           |

| 3.  | Remove Null Pointer checks        | Points-to analysis           |

| 4.  | Loop parallelization              | Dependence analysis          |

| 5.  | Remove array out of bounds checks | Bounds check                 |

| 6.  | Debugging                         | Program slice                |

| 7.  | Register allocation               | Liveness analysis            |

| 8.  | Find-definition (IDE)             | Def-use analysis             |

| 9.  | Dead-code elimination             | Reaching-definition analysis |

| 10. | Program-safety                    | Type checking                |

| 11. | Barrier elimination               | MHP Analysis                 |

| 12. | Race Detection                    | MHP Analysis                 |

|     |                                   |                              |

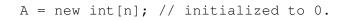

### Why Parallel Program Analysis?

- Parallel systems have become mainstay (Why? holdon).

- Automatic Extraction of parallelism has not been very successful.

- The community is looking at writing parallel programs.

- Analysis of parallel programs is a natural consequence.

# Why Parallel Systems / Multicores?

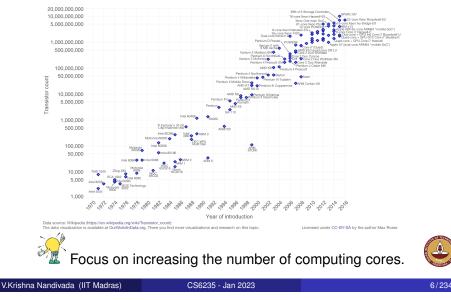

Moore's Law – The number of transistors on integrated circuit chips (1971-2016) Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important as other aspects of technological progress – such as processing speed or the price of electronic products – are strongly linked to Moore's law.

# V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023 5/234

### What, When Multicores? Why not Multiprocessors

- What A multi-core processor is composed of two or more independent cores. Composition involves the interconnect, memory, caches.

- When IBM POWER4, the world's first dual-core processor, released in 2001.

- Why not Multi-processors

- An application can be "threaded" across multiple cores, but not across multi-CPUs – communication across multiple CPUs is fairly expensive.

- Some of the resources can be shared. For example, on Intel Core Duo: L2 cache is shared across cores, thereby reducing further power consumption.

- Less expensive: A single CPU board with a dual-core CPU Vs a dual board with 2 CPUs.

# Course outline

- A rough outline (we may not strictly stick to this).

- Parallel programming constructs basics.

- Program analysis basics

- Parallel program representation

- MHP analysis and its impact on traditional analysis

- Parallel-Program Specific analysis

- Advanced Topics (depending on time).

### Start exploring

- Java familiarity a must Use eclipse to save you valuable coding and debugging cycles.

- JavaCC, JTB tools you will learn to use.

- Make Ant Scripts recommended toolkit.

- Find the course webpage: http://www.cse.iitm.ac.in/~krishna/cs6235/

Get set. Ready steady go!

### Expectations

What qualities are important in a program analysis?

- Should identify properties correctly.

- Should analyze all valid programs.

- Analysis runs fast

- Analysis time proportional to program size

- Support for modular analysis.

- 6

Each of these shapes your expectations about this course

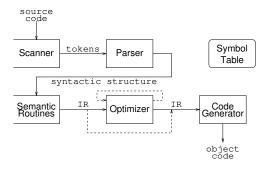

### Phases inside the compiler

V.Krishna Nandivada (IIT Madras)

character-stream Lexical Analyzer token-stream Syntax Analyzer syntak-tree Semantic Analyzer syntak-tree Intermediate Code Generator intermediate-tepresentation Machine-Independent Opt intermediate-tepresentation Code Generation target-machine-code (IR) Machine-dependent Opt target-machine-code

Front end responsibilities:

- Recognize syntactically legal code; report errors.

- Recognize semantically legal code; report errors.

- Produce IR.

CS6235 - Jan 2023

Back end responsibilities:

• Optimizations, code generation.

### **Program Analysis:**

After parsing.

**Parallel Programs:**

Impacts both FE and BE

```

function int Withdraw(int amount){

if (balance > amount) {

balance = balance - amount;

return SUCCESS;

}

return FAIL;

}

```

- Say balance = 100.

- Two parallel threads executing Withdraw(80)

- At the end of the execution, it may so happen that both of the withdrawals are successful. Further balance can still be 20!

```

V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023

```

```

Examples of how Parallelism Impacts Analysis II/III

```

```

for (int i = ...) {

X[f(i)] = ...;

async { ... = X[g(i)]; }

}

```

```

\implies // Legal transformation?

```

```

// After loop distribution

for (int i = ...)

X[f(i)] = ...;

for (int i = ...)

async { ... = X[g(i)]; }

```

### Race freedom is enough?

| <pre>void deposit(int amt)     acquire(m);     balance = balance+a     release(m); } int read_balance() {     int t;     acquire(m);     t = balance;     release(m);     return t;</pre> | <pre>int t = read_balance();</pre> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| }                                                                                                                                                                                         | }                                  |

| <pre>// Initial balance = fork withdraw(10); ; fork deposit(10); ;</pre>                                                                                                                  | 10.<br>// Thread 1<br>// Thread 2  |

| Example taken from Flanagan and                                                                                                                                                           | Qadeer TLDI 2003.                  |

| V.Krishna Nandivada (IIT Madras)                                                                                                                                                          | CS6235 - Jan 2023 14/234           |

|                                                                                                                                                                                           |                                    |

### Example of how Parallelism Impacts Analysis III/III

### Outline

### Introduction

- Formalities

- Overview

- Parallelism and its impact on performance

- Introduction Parallel constructs

- Java Concurrency

- Forward Analysis

- Backward Analysis (a brief overview)

- Dimensions of Analysis

- Points-to/Alias Analysis

- Dimensions of Analysis: Inter-/Intra- procedural

CS6235 - Jan 2023

- Call Graph Construction

- Dependence Analysis

- - Symbol Tables

- Intermediate Representation

V.Krishna Nandivada (IIT Madras)

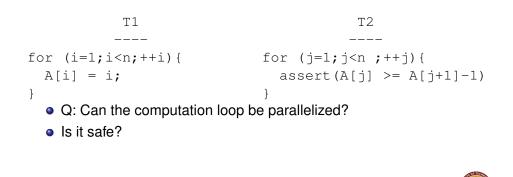

### Amdahl's Law

- Serial fraction  $\gamma = \frac{T_{setup} + T_{finalization}}{T_{total}(1)}$

- Fraction of time spent in parallelizable part =  $(1 \gamma)$

$$T_{total}(N) = \underbrace{\frac{\gamma \times T_{total}(1)}{\text{serial code}}}_{\text{serial code}} + \underbrace{\frac{(1-\gamma) \times T_{total}(1)}{N}}_{\text{parallel code}}$$

$$= \left(\gamma + \frac{1-\gamma}{N}\right) \times T_{total}(1)$$

Speedup  $S(N) = \frac{T_{total}(1)}{(\gamma + \frac{1-\gamma}{N}) \times T_{total}(1)}$

$$= \frac{1}{(\gamma + \frac{1-\gamma}{N})}$$

$$\approx \frac{1}{\gamma} \qquad \dots \text{Amdahl's Law}$$

• Max speedup is inversely proportional to the serial fraction of the code.

17/234

### Sources of speedups in Parallel Programs

- Say a serial Program *P* takes *T* units of time.

- Q: How much time will the best parallel version P' take (when run on N number of cores)?  $\frac{T}{N}$  units?

- Linear speedups is almost unrealizable, especially for increasing number of compute elements.

- $T_{total} = T_{setup} + T_{compute} + T_{finalization}$

- T<sub>setup</sub> and T<sub>finalization</sub> may not run concurrently represent the execution time for the non-parallelizable parts of code.

- Best hope : *T<sub>compute</sub>* can be fully parallelized.

- $T_{total}(N) = T_{setup} + \frac{T_{compute}}{N} + T_{finalization} \dots \dots \dots (1)$

- Speedup  $S(N) = \frac{T_{total}(1)}{T_{total}(N)}$ . In practice?

- Chief factor in performance improvement : Serial fraction of the code.

CS6235 - Jan 2023

V.Krishna Nandivada (IIT Madras)

18/234

### Implications of Amdahl's law

Assume: Ten processors. Goal: 10 fold speedup.

| Serial fraction | Parallel fraction | Speedup = $\frac{1}{\left(\gamma + \frac{1-\gamma}{N}\right)}$ |

|-----------------|-------------------|----------------------------------------------------------------|

| 40 %            | 60 %              | 2.17                                                           |

| 20 %            | 80 %              | 3.57                                                           |

| 10 %            | 90 %              | 5.26                                                           |

| 01 %            | 99 %              | 9.17                                                           |

### Implications of Amdahl's law

- As we increase the number of parallel compute units, the speed up need not increase - an upper limit on the usefulness of adding more parallel execution units.

- For a given program maximum speedup nearly remains a constant.

- Say a parallel program spends only 10% of time in parallelizable code. If the code is fully parallelized, as we aggressively increase the number of cores, the speedup will be capped by (~) 1.11×.

- Say a parallel program spends only 10% of time in parallelizable code. Q: How much time would you spend to parallelize it?

- Amdahl's law helps to set realistic expectations for performance gains from the parallelization exercise.

- Mythical Man-month Essays on Software Engineering. Frederic Brooks.

CS6235 - Jan 2023

• An over approximation : In reality many factors affect the

parallelization and even fully parallelizable code does not result in

• Does not say anything about the impact of cache - may result in

parallelization in result in faster execution of the serial code?

• Amdahl's law assumes that the problem size remains the same

• Dependence of the serial code on the parallelizable code - can the

V.Krishna Nandivada (IIT Madras)

V.Krishna Nandivada (IIT Madras)

Limitations of Amdahl's law

Overheads exist in parallel task

creations/termination/synchronization.

much more or far less improvements.

linear speed ups.

### CS6235 - Jan 2023

### 23/234

21/234

### Peaking via Amdahl's law

### Discussion: Amdahl's Law

- When we increase the number of cores the problem size is also increased in practise.

- Also, naturally we use more and more complex algorithms, increased amount of details etc.

- Given a fixed problem, increasing the number of cores will hit the limits of Amdahl's law. However, if the problem grows along with the increase in the number of processors Amdahl's law would be pessimistic

- Q: Say a program *P* has been improved to *P'* (increase the problem size) how to keep the running time same? How many parallel compute elements do we need?

### Outline

### 1 Introduction

- Formalities

- Overview

- Parallelism and its impact on performance

### Introduction Parallel constructs

Java Concurrency

- Forward Analysis

- Backward Analysis (a brief overview)

- Dimensions of Analysis

- Points-to/Alias Analysis

- Dimensions of Analysis: Inter-/Intra- procedural

CS6235 - Jan 2023

- Call Graph Construction

- Dependence Analysis

- 3 Symbol Tables and Intermediate Representation

- Symbol Tables

- Intermediate Representation

### V.Krishna Nandivada (IIT Madras)

Deadlock Analysis

### **Processes - Example**

```

int *y;

void main() {

int done = 0;

y=calloc(1,4);

printf("1. Before forking\n");

if (fork() == 0) {

printf("2a. In the Child\n");

done = 1;

while (*v == 0);

What is the output?

printf("2b. Ending the Child\n");

exit(0);

} else {

printf("3a. After forking\n");

while (!done) ;

*y = 1;

printf("3b. Before waiting\n");

wait();

}

printf("4. Bye\n"); }

V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

```

### Concurrency in programs

|         | Processes                                    | Threads                                 | Tasks                                            |

|---------|----------------------------------------------|-----------------------------------------|--------------------------------------------------|

| 1       | A program in exe-<br>cution                  | Light weight process                    | sequence of instruc-<br>tions                    |

| 2       | Shared mem:<br>1 process/run                 | 1 or more threads per<br>process        | one more tasks can<br>be executed by a<br>thread |

| 3       | Distributed mem:<br>1 or more pro-<br>cesses | 1 or more threads per<br>process        | one more tasks can<br>be executed by a<br>thread |

| 4       | C:fork                                       | Java:new Thread()<br>C:pthread_create() | X10: async S                                     |

| 5.      | Does NOT share<br>heap/stack                 | Shares Heap                             | Share stack + heap                               |

| 6.      | Scheduled by the OS                          | Scheduled by the run-<br>time           | Scheduled by the threads/runtime                 |

| V.Krisl | hna Nandivada (IIT Madras)                   | CS6235 - Jan 2023                       | 26/234                                           |

### Threads - Example

```

int *y;

void main() {

int done = 0;

y=calloc(1,4);

printf("1. Before forking\n");

if (create_thread() == 0) { // hypothetical call

printf("2a. In the Childn");

done = 1;

while (*v == 0);

What is the output?

printf("2b. Ending the Child\n");

} else {

```

CS6235 - Jan 2023

```

printf("3a. After creating thread\n");

while (!done) ;

*y = 1;

printf("3b. Before waiting\n");

wait();

}

printf("4. Bye\n"); }

```

27/234

25/234

### Tasks - Example

```

int *y;

void main() {

int done = 0;

y=calloc(1, 4);

printf("1. Before forking\n");

async{ // create task

printf("2a. In the Child\n");

done = 1;

while (*y == 0);

What is the output?

printf("2b. Ending the Child\n");

printf("3a. After creating task\n");

while (!done) ;

*y = 1;

printf("3b. Before waiting\n");

wait();

printf("4. Bye\n"); }

```

### Operations on or by processes / threads /tasks

- Creation.

- Execute in parallel with each other.

- May communicate with each other (data / synchronization).

CS6235 - Jan 2023

• Termination.

V.Krishna Nandivada (IIT Madras)

```

V.Krishna Nandivada (IIT Madras)

```

CS6235 - Jan 2023

### Outline

### 1 Introduction

- Formalities

- Overview

- Parallelism and its impact on performance

- Introduction Parallel constructs

### • Java Concurrency

### Program Analysis Basics

- Forward Analysis

- Backward Analysis (a brief overview)

- Dimensions of Analysis

- Points-to/Alias Analysis

- Dimensions of Analysis: Inter-/Intra- procedural

- Call Graph Construction

- Dependence Analysis

- Symbol Tables and Intermediate Representation

- Symbol Tables

- Intermediate Representation

31/234

29/234

### Java Threads Vs Processes

- Each instance of JVM creates a single process.

- Each process creates one or more threads.

- Main thread creates the others.

- Each Java thread is an object instance of the Java Thread class.

- An application that creates an instance of Thread must provide the code that will run in that thread.

- implement Runnable interface.

- Provide an implementation of the run method.

or

• extend Thread **class**

• Provide an overridden implementation of the run method. Adv/Disadv??

- (Hint) Java allows single inheritance.

- Extending thread class  $\Rightarrow$  cannot extend any other class.

# V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023 33/234

### Communication via synchronized methods

- synchronized statements and methods. Making a methods synchronized has two effects:

- It is not possible for two invocations of synchronized methods on the same object to interleave.

- When a synchronized method exits, it automatically establishes a happens-before relationship with any subsequent invocation of a synchronized method for the same object.

- Guarantees that changes to the state of the object are visible to all threads.

- Constructors cannot be synchronized. Why? Consequence only the object creating threads should call the constructor.

- synchronized methods ensure that there is no thread interference.

- Q: Too many synchronized methods. Disadv?

- Start executing the thread body specified in the run method.

- Sleep Thread.sleep(..)

What can a thread do?

- Wait for child threads to finish: ch.join()

- Communicate with other threads.

CS6235 - Jan 2023

### How do synchronized methods/statements work?

- Each object has an associated intrinsic lock.

- When a thread invokes a synchronized method,

- automatically acquires the intrinsic lock for that method's object

- releases the lock when the method returns (normal or via exception).

- What if a thread invokes a synchronized method recursively?

Java guarantees that following actions would be atomic.

- Reads and writes are atomic for reference variables and for most primitive variables (all types except long and double).

- Reads and writes are atomic for all variables declared volatile (including long and double variables).

- Any write to a volatile variable establishes a happens-before relationship with subsequent reads of that same variable.

- We can also declare a variable (of some types) as atomic.

### Atomic variables

- The java.util.concurrent.atomic package defines classes supporting atomic operations on single variables.

- Supports many types of get and set operations.

- Like volatile variables' write operation, the set operation has an happens-before relation with the corresponding get operation.

# VKrishna Nandivada (IIT Madras) CS6235 - Jan 2023 37/234 VKrishna Nandivada (IIT Madras) CS6235 - Jan 2023 Atomic variables - Example Atomic variables (contd) import java.util.concurrent.atomic.AtomicInteger; AtomicCounter { • Supported classes: private AtomicInteger c = new AtomicInteger(0); // guarantees thread non-interference. • Supported classes: AtomicBoolean AtomicInteger AtomicInteger

// guarantees thread non-interference

public void increment() {

c.incrementAndGet();

}

public void decrement() {

c.decrementAndGet();

}

public int value() {

return c.get();

}

| <ul> <li>Supported classe</li> </ul> | S:              |                    |

|--------------------------------------|-----------------|--------------------|

| AtomicBoolean                        | AtomicInteger   | AtomicIntegerArray |

|                                      | AtomicLong      | AtomicLongArray    |

|                                      | LongAccumulator | LongAdder          |

| • All support: bool                  | ean compareAndS | et (expectedValue. |

- All support: boolean compareAndSet (expectedValue, updateValue)

- CAS operation: How to use it to realize synchronization?

- Building blocks for implementing 'non-blocking' data structures.

### Happens before relation

- Sequential order: Each action in a thread happens-before every action in that thread that comes later in the program's order.

- Unlock → Lock: An unlock (synchronized block or method exit) of a monitor happens-before every subsequent lock (synchronized block or method entry) of that same monitor.

- Volatile writes: A write to a volatile field happens-before every subsequent read of that same field. Writes and reads of volatile fields have similar memory consistency effects as entering and exiting monitors, but do not entail mutual exclusion locking.

- A call to start on a thread happens-before any action in the started thread.

- All actions in a thread happen-before any other thread successfully returns from a join on that thread.

Happens-before relation is transitive.

```

V.Krishna Nandivada (IIT Madras)

```

CS6235 - Jan 2023

### Guarded blocks

A way to coordinate with others.

A guarded block

polls a condition that has to be true to proceed.

other threads set that condition

public void guardedEntry() {

while (!flag);

```

// flag is set. Inefficient.

```

```

Deadlock, Livelock and Starvation

```

- Deadlock: two or more threads are blocked forever, waiting for each other.

- Starvation: a thread is unable to gain regular access to shared resources and is unable to make progress.

- Livelock: threads are not blocked, but are not making any progress.

### V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

and and

### Guarded blocks (contd)

```

public synchronized void guardedEntry() {

// Check once and "wait"

while(!flag) { // Loop is needed.

try {

wait(); // releases the lock

} catch (InterruptedException e) {}

}

// flag is set. Efficient.

}

```

- Q: Why synchronized?

- notify **VS** notifyAll

### **Immutable Objects**

- An object is considered immutable if its state cannot change after it is constructed.

- Helps write reliable code.

- cannot be corrupted by thread interference or observed in an inconsistent state.

- Creating many immutable objects Vs updating existing objects.

- Cost of object creation, GC

- Code needed to protect mutable objects from corruption.

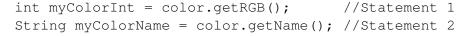

### Example (contd)

| • • •                   |      |      |           |

|-------------------------|------|------|-----------|

| SynchronizedRGB color = |      |      |           |

| new SynchronizedRGB(    | 0, 0 | , 0, | "Black"); |

### What if another threads updates the color object after Statement 1?

```

synchronized (color) {

int myColorInt = color.getRGB();

String myColorName = color.getName();

}

```

### Such issues do not arise with immutable objects

### Example

```

public class SynchronizedRGB {

private int red; // between 0 - 255.

private int green; // between 0 - 255.

private int blue; // between 0 - 255.

private String name;

public synchronized void set(int r, int g, int b,

String n) {..}

public synchronized int getRGB() {

return ((red << 16) | (green << 8) | blue);

public synchronized String getName() { return name; }

public synchronized void invert() {

red=255-red; green=255-green; blue=255-blue;

name="Inverse of " + name;

} }

V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

```

### Mutable to Immutable

General guidelines:

- Don't provide 'setter' methods.

- Make all fields final and private.

- Don't allow subclasses to override methods or provide 'setter' methods.

- declare the class as final.

- make constructor final and provide a factory method.

- If the instance fields include references to mutable objects, don't allow those objects to be changed:

- Don't provide methods that modify the mutable objects.

- Don't share references to the mutable objects. Copy and share if required.

### Mutable to Immutable (Example)

### final public class ImmutableRGB { final private int red; // between 0 - 255. final private int green; // between 0 - 255. final private int blue; // between 0 - 255. final private String name; public /\*synchronized\*/ int getRGB() { return ((red << 16) | (green << 8) | blue); } public /\*synchronized\*/ String getName() { return name; } public /\*synchronized\*/ ImmutableRGB invert() { return new ImmutableRGB(255 - red, 255 - green, 255 - blue, "Inverse of " + name); } } No synchronized methods required! V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023 49/234

### Deadlocks in Locks (contd)

```

public static void main(String[] args) {

final Friend alpha = new Friend("Alpha");

final Friend beta = new Friend("Beta");

new Thread(new Runnable() {

public void run() { alpha.bow(beta); }

}).start();

new Thread(new Runnable() {

public void run() { beta.bow(alpha); }

}).start();

}

```

### Deadlocks in Locks

```

public class Deadlock {

class Friend {

private final String name;

public Friend(String name) {this.name = name; }

public String getName() {return this.name; }

public synchronized void bow(Friend bower) {

System.out.format("%s: %s" +" has bowed to me!",

this.name, bower.getName());

bower.bowBack(this); }

public synchronized void bowBack(Friend bower) {

System.out.format("%s:%s"+" has bowed back!",

this.name, bower.getName()); }

```

CS6235 - Jan 2023

```

V.Krishna Nandivada (IIT Madras)

```

```

E CARACTERISTIC

```

### Avoid deadlocks in Locks

```

import java.util.concurrent.locks.Lock;

import java.util.concurrent.locks.ReentrantLock;

import java.util.Random;

public class Safelock {

static class Friend {

private final String name;

private final Lock lock = new ReentrantLock();

public Friend(String name) { this.name=name; }

public String getName() { return this.name; }

```

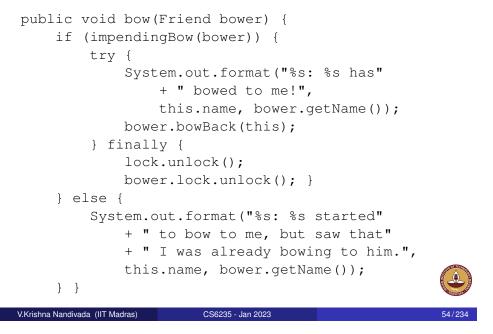

### Avoid deadlocks in Locks (cont.)

```

public boolean impendingBow(Friend bower) {

Boolean myLock = false;

Boolean yourLock = false;

try {

myLock = lock.tryLock();

yourLock = bower.lock.tryLock();

} finally {

if (! (myLock && yourLock)) {

if (myLock) {

lock.unlock();

}

if (yourLock) {

bower.lock.unlock();

} } }

return myLock && yourLock;

V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

53/234

```

### Avoid deadlocks in Locks (cont.)

```

public void bowBack(Friend bower) {

System.out.format("%s: %s has" +

" bowed back to me!%n",

this.name, bower.getName());

}

```

### Avoid deadlocks in Locks (cont.)

### Avoid deadlocks in Locks (cont.)

```

class BowLoop implements Runnable {

private Friend bower;

private Friend bowee;

public BowLoop(Friend bower, Friend bowee) {

this.bower = bower; this.bowee = bowee;}

public void run() {

Random random = new Random();

for (;;) {

try {

Thread.sleep(random.nextInt(10));

} catch (InterruptedException e) {}

bowee.bow(bower);

} }

}

}

```

```

public static void main(String[] args) {

final Friend alpha = new Friend("Alpha");

final Friend beta = new Friend("Beta");

new Thread(new BowLoop(alpha, beta)).start();

new Thread(new BowLoop(beta, alpha)).start();

}

```

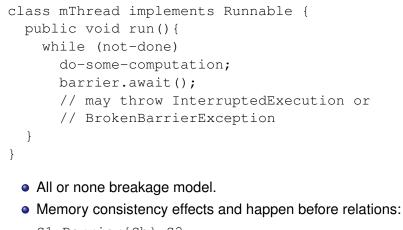

• CyclicBarrier

V.Krishna Nandivada (IIT Madras)

- allows a set of threads to wait for each other.

- can be reused after the end of one phase.

57/234

V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023

### Barriers in Java (cont.)

```

S1 Barrier{Sb} S2

S3 Barrier{Sb} S4

```

S1 and S3 happen before Sb and Sb happens before S2 and S

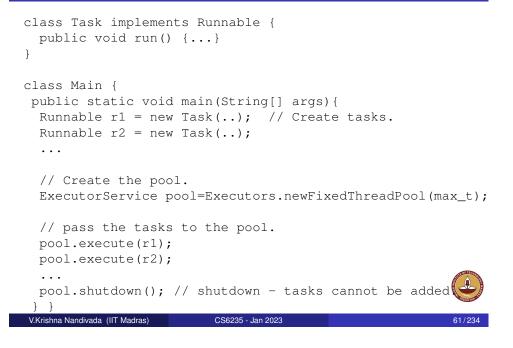

### Tasks and ThreadPools in Java

• ThreadPool: reuses previously created threads to execute current tasks

CS6235 - Jan 2023

- Threads are created once and reused across all the tasks.

- Less overhead.

- When task/tasks arrive(s), the threads are ready.

- Avoids resource thrashing caused by creating threads arbitrarily.

### ThreadPools and Tasks example

### **Program Analysis**

- Code optimization requires that the compiler has a global "understanding" of how programs use the available resources.

- It has to understand how the control flows (control-flow analysis) in the program and how the data is manipulated (data-flow analysis)

- Control-flow analysis: flow of control within each procedure and across procedures.

- Data-flow analysis: how the data is manipulated in the program.

63/234

### Outline

- Introduction

- Formalities

- Overview

- Parallelism and its impact on performance

- Introduction Parallel constructs

- Java Concurrency

### 2 Program Analysis Basics

- Forward Analysis

- Backward Analysis (a brief overview)

- Dimensions of Analysis

- Points-to/Alias Analysis

- Dimensions of Analysis: Inter-/Intra- procedural

- Call Graph Construction

- Dependence Analysis

- Symbol Tables and Intermediate Representation

- Symbol Tables

- Intermediate Representation

V.Krishna Nandivada (IIT Madras) Deadlock Analysis

Memory consistency models

### Example

| int fib (int m){                                            | 1        | receive m (val)     |

|-------------------------------------------------------------|----------|---------------------|

| int f0=0, f1=1, f2,i;                                       | 2        | f0 = 0              |

| if (m <=1)                                                  | 3        | f1 = 1              |

| return m;                                                   | 4        | if (m <= 1) goto L3 |

| else {                                                      | 5        | i = 2               |

| for (i=2; i<=m; ++i) {                                      | 6 L1:    | if (i<=m) goto L2   |

| f2 = f0 + f1;                                               | 7        | return f2           |

| f0 = f1;                                                    | 8 L2:    | f2 = f0 + f1        |

| f1 = f2;                                                    | 9        | f0 = f1             |

| }                                                           | 10       | f1 = f2             |

| return f2;                                                  | 11       | i = i + 1           |

| }                                                           | 12       | goto Ll             |

| }                                                           | 13 L3    | :return m           |

| <ul> <li>IR for the C code (in a format describe</li> </ul> | ed in Mu | chnick book)        |

| • reactive specifies the reception of a                     | naramo   | tor and the         |

receive specifies the reception of a parameter and the parameter-passing discipline (by-value, by-result, value-result, reference). Why do we want to have an explicit receive instruction?– Gives a point of definition for the args.

### Example - flow chart and control-flow

| int fib (int m){       | 1 receive m (val)       |

|------------------------|-------------------------|

| int f0=0, f1=1, f2,i;  | 2 	f 0 = 0              |

| if (m <=1)             | 3 f1 = 1                |

| return m;              | 4 if (m <= 1) goto L3   |

| else {                 | 5 i = 2                 |

| for (i=2; i<=m; ++i) { | 6 L1: if (i<=m) goto L2 |

| f2 = f0 + f1;          | 7 return f2             |

| f0 = f1;               | 8 L2: $f2 = f0 + f1$    |

| f1 = f2;               | 9 $f0 = f1$             |

| }                      | 10 f1 = f2              |

| return f2;             | 11 i = i + 1            |

| }                      | 12 goto L1              |

| }                      | 13 L3:return m          |

- The high-level abstractions might be lost in the IR.

- Control-flow analysis can expose control structures not obvious in the high level code. Possible? Loops constructed from if and goto

- A basic block is informally a straight-line sequence of code that can be entered only at the beginning and exited only at the end.

```

V.Krishna Nandivada (IIT Madras)

```

```

CS6235 - Jan 2023

```

### Deep dive - Basic block

Basic block definition

- A basic block is a maximal sequence of instructions that can be entered only at the first of them

- The basic block can be exited only from the last of the instructions of the basic block.

- Implication: First instruction can be a) entry point of a routine, b) item target of a branch, c) item instruction following a branch or a return.

- First instruction is called the leader of the BB.

### How to construct the basic block?

- Identify all the leaders in the program.

- For each leader: include in its basic block all the instructions from the leader to the next leader (next leader not included) or the end of the routine, in sequence.

What about function calls?

- In most cases it is not considered as a branch+return. Why?

- Problem with setjmp() and longjmp()? [self-study ] CS6235 - Jan 2023

### Basic blocks - what do we get?

66/234

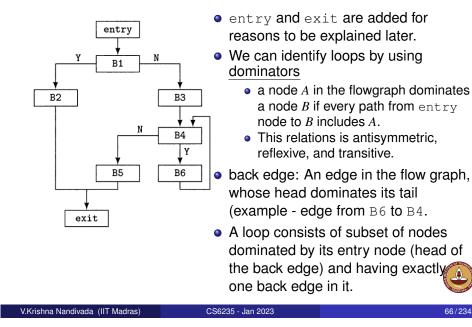

### CFG - Control flow graph

Definition:

65/234

- A rooted directed graph G = (N, E), where N is given by the set of basic blocks + two special BBs: entry and exit.

- And edge connects two basic blocks  $b_1$  and  $b_2$  if control can pass from  $b_1$  to  $b_2$ .

- An edge(s) from entry node to the initial basic block(s?)

- From each final basic blocks (with no successors) to exit BB.

- successor and predecessor defined in a natural way.

- A basic block is called branch node if it has more than one successor.

- join node has more than one predecessor.

- For each basic block *b*:

$Succ(b) = \{n \in N | \exists e \in E \text{ such that } e = b \to n\}$  $Pred(b) = \{n \in N | \exists e \in E \text{ such that } e = n \to b\}$

• A region is a strongly connected subgraph of a flow-graph.

### **Reaching Definitions**

A particular definition of a variable is said to reach a given point if

• there is an execution path from the definition to that point

• the variable might <u>may</u> have the value assigned by the definition. In general undecidable.

### Our goal:

- The analysis must be conservative the analysis should not tell us that a particular definition does not reach a particular use, if it may reach.

- A 'may' conservative analysis gives us a larger set of reaching definitions than it might, if it could produce the minimal result.

To make maximum benefit from our analysis, we want the analysis to be conservative, but be as aggressive as possible.

**Data Flow Analysis**

### Why:

- Provide information about a program manipulates its data.

- Study function's behavior.

- To help build control flow information.

- Program understanding (a function sorts an array!).

- Generating a model of the original program and verify the model.

- The DFA should give information about that program that does not misrepresent what the procedure being analyzed does.

- Program validation.

CS6235 - Jan 2023

### Different types of analysis

- Intra procedural analysis.

- Whole program (inter-procedural) analysis.

- Generate intra procedural analysis and extend it to whole program.

- We will study an iterative mechanism to perform such analyses.

### Iterative Dataflow Analysis

- Build a collection of data flow equations specifying which data may flow to which variable.

- Solve it iteratively.

- Start from a conservative set of initial values and continuously improve the precision.

Disadvantage: We may be handling large data sets.

Start from an aggressive set of initial values – and continuously improve the precision.

Advantage: Datasets are small to start with.

• Choice – depends on the problem at hand.

|                                  |                   | 2      |

|----------------------------------|-------------------|--------|

| V.Krishna Nandivada (IIT Madras) | CS6235 - Jan 2023 | 73/234 |

|                                  |                   |        |

### Definitions

- GEN : GEN(b) returns the set of definitions generated in the basic block b; assigned values in the block and not subsequently killed in it.

- KILL : KILL(b) returns the set of definitions killed in the basic block b.

- IN : IN(b) returns the set of definitions reaching the basic block b.

- OUT : OUT(b) returns the set of definitions going out of basic block b.

- PRSV : Negation of KILL

# Example program

1 int q (int m, int i); 2 int f(int n)3 int i = 0, j;4 if (n == 1) i = 2; 5 while (n > 0) { 6 j = i + 1;7 n = q(n, i);8 } 9 return j; 10 }

• Does def of i in line 3 reach the uses in line 6 and 7?

• Does def of j in line 6 reach the use in line 9?

V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

74/234

### Representation and Initialization

| 1 receive m (val)                                                                                                                                | Bit Pos | Definition     | Basic Block |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|-------------|

|                                                                                                                                                  | 1       | m in node 1    | B1          |

| $2 \qquad f_0 \leftarrow 0$                                                                                                                      | 2       | f0 in node 2   |             |

| $3 \qquad f1 \leftarrow 1$                                                                                                                       | 3       | f1 in node 3   |             |

| Y m <= 1 N                                                                                                                                       | 4       | i in node 5    | B3          |

|                                                                                                                                                  | 5       | f2 in node 8   | B6          |

| 12 return m 5 i ← 2                                                                                                                              | 6       | f0 in node 9   |             |

| N i <= m                                                                                                                                         | 7       | f1 in node 10  |             |

| $\begin{array}{c c} & & & \\ & & & \\ \hline 7 & \text{return } f2 \\ \end{array} \qquad 8 & \hline f2 \leftarrow f0 + f1 \\ \hline \end{array}$ | 8       | i in node 11   |             |

|                                                                                                                                                  |         | Set rep        | Bit vector  |

| 9 <u>f0 ← f1</u>                                                                                                                                 | GEN(B1) | = {1, 2, 3}    | (11100000)  |

| $10  f1 \leftarrow f2$                                                                                                                           | GEN(B3) | = {4}          | (00010000)  |

| <b>1</b> 1 ↓ <b>1</b> 1                                                                                                                          | GEN(B6) | = {5, 6, 7, 8} | (00001111)  |

|                                                                                                                                                  | GEN(.)  | = {}           | (00000000)  |

|          | Set rep                    | Bit vector                 |

|----------|----------------------------|----------------------------|

| PRSV(B1) | = {4, 5, 8}                | <pre>(00011001)</pre>      |

| PRSV(B3) | = {1, 2, 3, 5, 6, 7}       | $\langle 11101110 \rangle$ |

| PRSV(B6) | = {1}                      | $\langle 1000000 \rangle$  |

| PRSV(.)  | = {1, 2, 3, 4, 5, 6, 7, 8} | $\langle 11111111 \rangle$ |

### Solving the Dataflow equations: example

Itr 1:

Itr 2:

| OUT(entry)                                                                                                                               | $=\langle 00000000 \rangle$                                                                                                                      | IN(entry)                                      | $=\langle 00000000 \rangle$                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT(B1)                                                                                                                                  | $=\langle 11100000\rangle$                                                                                                                       | IN(B1)                                         | $=\langle 00000000 \rangle$                                                                                                                          |

| OUT(B2)                                                                                                                                  | $=\langle 11100000\rangle$                                                                                                                       | IN(B2)                                         | $=\langle 11100000 \rangle$                                                                                                                          |

| OUT(B3)                                                                                                                                  | $=\langle 11110000\rangle$                                                                                                                       | IN(B3)                                         | $=\langle 11100000 \rangle$                                                                                                                          |

| OUT(B4)                                                                                                                                  | $=\langle 11110000\rangle$                                                                                                                       | IN(B4)                                         | $=\langle 11110000 \rangle$                                                                                                                          |

| OUT(B5)                                                                                                                                  | $=\langle 11110000\rangle$                                                                                                                       | IN(B5)                                         | $=\langle 11110000\rangle$                                                                                                                           |

| OUT(B6)                                                                                                                                  | $=\langle 00001111\rangle$                                                                                                                       | IN(B6)                                         | $=\langle 11110000\rangle$                                                                                                                           |

| OUT(entry)                                                                                                                               | $=\langle 11110000\rangle$                                                                                                                       | IN(exit)                                       | $=\langle 11110000\rangle$                                                                                                                           |

|                                                                                                                                          |                                                                                                                                                  |                                                |                                                                                                                                                      |

|                                                                                                                                          |                                                                                                                                                  |                                                |                                                                                                                                                      |

| OUT(entry)                                                                                                                               | $=\langle 00000000 \rangle$                                                                                                                      | IN(entry)                                      | $=\langle 00000000 \rangle$                                                                                                                          |

| OUT(entry)<br>OUT(B1)                                                                                                                    | $= \langle 00000000 \rangle$ $= \langle 11100000 \rangle$                                                                                        | IN(entry)<br>IN(B1)                            | $= \langle 00000000 \rangle \\ = \langle 00000000 \rangle$                                                                                           |

| ( )                                                                                                                                      | ( /                                                                                                                                              | ( ))                                           | ( /                                                                                                                                                  |

| OUT(B1)                                                                                                                                  | $=\langle 11100000 \rangle$                                                                                                                      | IN(B1)                                         | $=\langle 00000000 \rangle$                                                                                                                          |

| OUT(B1)<br>OUT(B2)                                                                                                                       | $= \langle 11100000 \rangle \\ = \langle 11100000 \rangle$                                                                                       | IN(B1)<br>IN(B2)                               | $= \langle 00000000 \rangle \\ = \langle 11100000 \rangle$                                                                                           |

| OUT(B1) $OUT(B2)$ $OUT(B3)$                                                                                                              | $= \langle 11100000 \rangle \\ = \langle 11100000 \rangle \\ = \langle 111100000 \rangle \\$                                                     | IN(B1)<br>IN(B2)<br>IN(B3)                     | $= \langle 00000000 \rangle$ $= \langle 11100000 \rangle$ $= \langle 11100000 \rangle$                                                               |

| <i>OUT</i> ( <i>B</i> 1)<br><i>OUT</i> ( <i>B</i> 2)<br><i>OUT</i> ( <i>B</i> 3)<br><i>OUT</i> ( <i>B</i> 4)                             | $= \langle 11100000 \rangle \\= \langle 11100000 \rangle \\= \langle 11100000 \rangle \\= \langle 111110000 \rangle \\= \langle 1111111 \rangle$ | IN(B1)<br>IN(B2)<br>IN(B3)<br>IN(B4)           | $= \langle 00000000 \rangle \\ = \langle 11100000 \rangle \\ = \langle 11100000 \rangle \\ = \langle 11111111 \rangle$                               |

| <i>OUT</i> ( <i>B</i> 1)<br><i>OUT</i> ( <i>B</i> 2)<br><i>OUT</i> ( <i>B</i> 3)<br><i>OUT</i> ( <i>B</i> 4)<br><i>OUT</i> ( <i>B</i> 5) | $= \langle 11100000 \rangle \\= \langle 11100000 \rangle \\= \langle 11110000 \rangle \\= \langle 1111111 \rangle \\= \langle 1111111 \rangle$   | IN(B1)<br>IN(B2)<br>IN(B3)<br>IN(B4)<br>IN(B5) | $= \langle 00000000 \rangle \\ = \langle 11100000 \rangle \\ = \langle 11100000 \rangle \\ = \langle 11111111 \rangle \\ = \langle 11111111 \rangle$ |

### **Dataflow equations**

A definition may reach the end of a basic block *i*:

$$OUT(i) = GEN(i) \cup (IN(i) \cap PRSV(i))$$

or with bit vectors:

$$OUT(i) = GEN(i) \lor (IN(i) \land PRSV(i))$$

A definition may reach the beginning of a basicblock *i*:

$IN(i) = \bigcup OUT(j)$  $j \in Pred(i)$

CS6235 - Jan 2023

- GEN, PRSV and OUT are created in each basic block.

- $OUT(i) = \{\} // initialization$

- But IN needs to be initialized to something safe.

- $IN(entry) = \{\}$

V.Krishna Nandivada (IIT Madras)

### Dataflow equations: behavior

- We specify the relationship between the data-flow values before and after a block - transfer or flow equations.

- Forward:  $OUT(s) = f(IN(s), \cdots)$

- Backward:  $IN(s) = f(OUT(s), \cdots)$

- The rules never change a 1 to 0. They may only change a 0 to a 1.

- They are monotone.

- Implication the iteration process will terminate.

- Q: What good is reaching definitions? undefined variables.

- Q: Why do the iterations produce an acceptable solution to the set of equations? - lattices and fixed points.

78/234

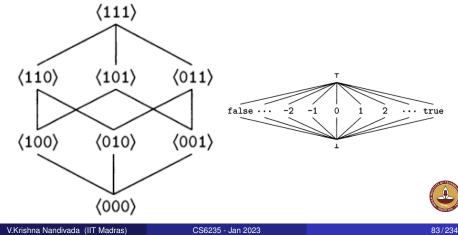

- What : Lattice is an algebraic structure

- Why : To represent <u>abstract</u> properties of variables, expressions, functions, etc etc.

- Values

- Attributes

- ...

- Why "abstract"? Exact interpretation (execution) gives exact values, abstract interpretation gives abstract values.

| V.Krishna Nandivada (IIT Madras) | CS6235 - Jan 2023 | 81/234 |

|----------------------------------|-------------------|--------|

|                                  |                   |        |

### Lattice properties

- Meet (and join) induce a partial order ( $\sqsubseteq$ ):  $\forall x, y \in L, x \sqsubseteq y$ , iff  $x \sqcap y = x$ .

- Transitive, antisymmetry and reflexive.

Example Lattices:

### Lattice definition

A lattice *L* consists of a set of values, and two operations called *meet* ( $\Box$ ) and *join* ( $\Box$ ). Satisfies properties:

- **closure**: For all  $x, y \in L$ ,  $\exists$  a unique z and  $w \in L$ , such that  $x \sqcup y = z$  and  $x \sqcap y = w$  each pair of elements have a unique <u>lub</u> and <u>glb</u>.

- **commutative**: For all  $x, y \in L$ ,  $x \sqcap y = y \sqcap x$ , and  $x \sqcup y = y \sqcup x$ .

- **associative**: For all  $x, y, z \in L$ ,  $(x \sqcap y) \sqcap z = x \sqcap (y \sqcap z)$ , and  $(x \sqcup y) \sqcup z = x \sqcup (y \sqcup z)$

- There exists two special elements of *L* called <u>bottom</u> ( $\perp$ ), and <u>top</u> ( $\top$ ).

- $\forall x \in L, x \sqcap \bot = \bot \text{ and } x \sqcup \top = \top.$

- **distributive** : (optional).  $\forall x, y, z \in L, x \sqcup (y \sqcap z) = (x \sqcup y) \sqcap (x \sqcup z)$ , and  $x \sqcap (y \sqcup z) = (x \sqcap y) \sqcup (x \sqcap z)$

V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

82/234

### Monotones and fixed point

- A function  $f : L \to L$ , is a monotone, if for all  $x, y \in L$ ,  $x \sqsubseteq y \Rightarrow f(x) \sqsubseteq f(y)$ .

- Example: bit-vector lattice:

- $f(x_1x_2x_3) = \langle x_1 1x_2 \rangle$

- $f(x_1x_2x_3) = \langle x_2x_3x_1 \rangle$

- A flow function models the effect of a programming language construct. as a mapping from the lattice for that particular analysis to itself.

- We want the flow functions to be monotones. Why?

- A fixed point of a function  $f: L \to L$  is an element  $z \in L$ , such that f(z) = z.

- For a set of data-flow equations, a fixed-point is a solution of the set of equations – cannot generate any further refinement.

### Meet Over All Paths solutions

- The value we wish to compute in solving data-flow equations is meet over all paths (MOP) solution.

- Start with some prescribed information at the <u>entry</u> (or <u>exit</u> depending on <u>forward</u> or <u>backward</u>).

- Repeatedly apply the composition of the appropriate flow functions.

- For each node form the meet of the results.

| V.Krishna Nandivada (IIT Madras) | CS6235 - Jan 2023 | 85/234 |

|----------------------------------|-------------------|--------|

### Example: Constant Propagation

Goal: Discover values that are constants on all possible executions of a program and to propagate these constant values as far forward through the program as possible

**Conservative**: Can discover only a subset of all the possible constants.

### Lattice:

### A worklist based implementation (a forward analysis)

1 procedure WorklistIterate (N: Set<Node>, entry: Node, F: Node  $\times L \rightarrow L$ , dfin: Node  $\rightarrow L$ , Init : L) // dfin is an output variable.

### 2 begin

- B, P: Node;

- worklist: Set<Node>;

effect, totalEffect : L;

- 5 effect, totalEffect :  $\int_{6} dfin(entry) \leftarrow Init;$

- 7 worklist =  $N \{entry\};$

- 8 foreach  $B \in N$  do dfin(B)  $\leftarrow \top$ ;

- 9 repeat

- 10  $B \leftarrow \text{worklist.removeOne()};$ 11 totalEffect  $\leftarrow \top;$

- 11 totalEffect  $\leftarrow \top$ ; 12 foreach P ∈ Pred(B) do

- 13 effect  $\leftarrow$  F(P, dfin(P));

- totalEffect ← totalEffect ⊓ effect;

- if  $\underline{dfin}(B) \neq totalEffect$  then

- 16  $dfin(B) \leftarrow totalEffect;$

- 17 worklist.add(Succ(B));

- 18 **until** worklist =  $\Phi$ ;

### V.Krishna Nandivada (IIT Madras)

### Constant Propagation lattice meet rules

CS6235 - Jan 2023

- $\perp$  = Constant value cannot be guaranteed.

- $\top$  = May be a constant, not yet determined.

- $\forall x$

- $x \sqcap \top = x$

- $x \sqcap \bot = \bot$

- $c_1 \sqcap c_1 = c_1$

- $c_2 \sqcap c_1 = \bot$

### Simple constant propagation

- Gary A. Kildall: A Unified Approach to Global Program Optimization - POPL 1973.

- Reif, Lewis: Symbolic evaluation and the global value graph POPL 1977.

- **Simple constant** Constants that can be proved to be constant provided,

- no information is assumed about which direction branches will take.

- Only one value of each variable is maintained along each path in the program.

### Constant propagation - equations

- Let us assume that one basic block per statement.

- Transfer functions set *F* a set of transfer functions.  $f_s \in F$  is the transfer function for statement *s*.

- The dataflow values are given by a map:  $m: Vars \rightarrow ConstantVal$

- If *m* is the set of input dataflow values, then m' = f<sub>s</sub>(m) gives the output dataflow values.

- Generate equations like before.

- Start with an entry node in the program graph.

- Process the entry node, and produce the constant propagation information. Send it to all the immediate successors of the entry node.

- At a merge point, get an intersection of the information.

- If at any successor node, if for any variable the value is "reduced", the process the successor, similar to the processing done for entry node.

### V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

### Constant propagation: equations (contd)

- Start with the entry node.

- If *s* is not an assignment statement, then *f<sub>s</sub>* is simply the identity function.

- If s is an assignment statement to variable v, then f<sub>s</sub>(m) = m', where:

- For all  $v' \neq v$ , m'(v') = m(v').

- If the RHS of the statement is a constant *c*, then m'(v) = c.

- If the RHS is an expression (say y op z),

$m'(v) = \begin{cases} m(y) \ op \ m(z) & \text{if } m(y) \ \text{and} \ m(z) \ \text{are constant values} \\ \bot & \text{if either of } m(y) \ \text{and} \ m(z) \ \text{is } \bot \\ \top & \text{Otherwise} \end{cases}$

- If the RHS is an expression that cannot be evaluated, then m'(v) = ⊥.

- At a merge point, get a meet of the flow maps.

### Constant Propagation - example I

| x = 10;          |

|------------------|

| y = 1;           |

| z = 5;           |

| if (cond) {      |

| y = y / x;       |

| x = x - 1;       |

| z = z + 1;       |

| } else {         |

| z = z + y;       |

| у = 0 <b>;</b>   |

| }                |

| print x + y + z; |

x = 10; y = 1; z = 1; while (x > 1) { y = x \* y; x = x - 1; z = z \* z; } A[x] = y + z;

### Outline

### Introduction

Formalities

V.Krishna Nandivada (IIT Madras)

- Overview

- Parallelism and its impact on performance

CS6235 - Jan 2023

- Introduction Parallel constructs

- Java Concurrency

### Program Analysis Basics

- Forward Analysis

- Backward Analysis (a brief overview)

- Dimensions of Analysis

- Points-to/Alias Analysis

- Dimensions of Analysis: Inter-/Intra- procedural

- Call Graph Construction

- Dependence Analysis

- Symbol Tables and Intermediate Representation

CS6235 - Jan 2023

- Symbol Tables

- Intermediate Representation

95/234

93/234

### Definitions

$a \leftarrow 0$

$c \leftarrow c + b$

$a \leftarrow b \times 2$

return c

if a < N goto  $L_1$

$L_1: b \leftarrow a+1$

A variable is <u>live</u> at a program point, if it holds a value that may be needed in future

CS6235 - Jan 2023

- v is live on edge e if there is a directed path from SRC(e) to a use of v that does not pass through any def(v)

- *v* is <u>live-in</u> at node *n* if live on all of *n*'s in-edges

- v is <u>live-out</u> at n if live on any of n's out-edges

- $v \in use[n] \Rightarrow v$  live-in at n

- *v* live-in at  $n \Rightarrow v$  live-out at all  $m \in pred[n]$

- *v* live-out at  $n, v \notin def[n] \Rightarrow v$  live-in at n

96/234

V.Krishna Nandivada (IIT Madras)

### Liveness analysis

Define:

$$in[n] =$$

variables live-in at  $n$

$out[n] =$  variables live-out at  $n$

Then:

$$out[n] = \bigcup_{s \in succ(n)} in[s]$$

$succ[n] = \phi \Rightarrow out[n] = \phi$

Note:

$$in[n] \supseteq use[n]$$

$in[n] \supseteq out[n] - def[n]$

CS6235 - Jan 2023

use[n] and def[n] are constant (independent of control flow) Now,  $v \in in[n]$  iff.  $v \in use[n]$  or  $v \in out[n] - def[n]$ Thus,  $in[n] = use[n] \cup (out[n] - def[n])$

V.Krishna Nandivada (IIT Madras)

### Flow Sensitive Vs Flow Insensitive

| i: | m | = | new | X(); | // | Ri |

|----|---|---|-----|------|----|----|

| j: | n | = | new | X(); | // | Rj |

| k: | р | = | m;  |      |    |    |

| 1: | р | = | n;  |      |    |    |

| a: | q | = | p;  |      |    |    |

| b: | n | = | m;  |      |    |    |

|    |   |   |     |      |    |    |

| Flow | sensitive | (after | 'b') | Flow | ir  |

|------|-----------|--------|------|------|-----|

| m -> | {Ri}      |        |      | m -> | { F |

| p -> | {Rj}      |        |      | p -> | { E |

| q -> | {Rj}      |        |      | q -> | { E |

| n -> | {Ri}      |        |      | n -> | { F |

| Flow | inse | nsitive: |

|------|------|----------|

| m -> | {Ri} |          |

| p -> | {Ri, | Rj}      |

| q -> | {Ri, | Rj}      |

| n -> | {Ri, | Rj}      |

|      |      |          |

# Iterative algorithm

Recall the iterative forward analysis and port it to perform backward analysis. [DIY]

### V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

98/234

100/234

### Outline

- - Formalities

- Overview

- Parallelism and its impact on performance

- Introduction Parallel constructs

- Java Concurrency

### Program Analysis Basics

- Forward Analysis

- Backward Analysis (a brief overview)

- Dimensions of Analysis

- Points-to/Alias Analysis

- Dimensions of Analysis: Inter-/Intra- procedural

- Call Graph Construction

- Dependence Analysis

- Symbol Tables

- Intermediate Representation

CS6235 - Jan 2023

99/234

### Points-to/Alias Analysis

Goal: Reason about what different variables / fields point to in the <u>heap</u>.

CS6235 - Jan 2023

```

p = new A(); // R1

p.f = new Y(); // R2

if (cond) {

q = new X(); // R3

q.f = new Z(); // R4

r1 = q;

} else {

q = new X(); // R5

q.f = new Z(); // R6

r2 = q;

}

p.f = new Y(); // R7

q.f = new Z(); // R8

```

### Points-to/Alias Analysis in Java

- Abstractly model Stack and Heap:

- Vars: Set of all Variables.

- Refs: Set of all References

- Values: P(Refs) // P = Power set

- Stack  $\rho$ : Vars  $\rightarrow$  Values

- Heap  $\sigma \text{:} \mbox{Refs} \times \mbox{Fields} \rightarrow \mbox{Values}$

- Initialize the Stack and Heap

- each local variable,

- fields (of the locally allocated objects)

- $\longrightarrow$  point to the empty set.

| V.Krishna Nandivada (IIT M | adras) CS6235 - Jan 2023 | 102/234 |

|----------------------------|--------------------------|---------|

# Points-to/Alias Analysis Lattice

### Points-to/Alias Analysis transfer functions

- L = Power set of all the abstract references.

- $x \sqcap y = x \cup y$

V.Krishna Nandivada (IIT Madras)

- $x \sqcup y = x \cap y$

- $\perp$  = Set of all the abstract references.

- $\top = \phi$

| 1.  | alloc                 | $a: x = new \dots$ $x = y$ $x = y.f$ $x.f = y$ $x = f = y$ | $\rho[x \leftarrow O_a]$                                                         |

|-----|-----------------------|------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.  | copy                  |                                                            | $\rho[x \leftarrow \rho(y)]$                                                     |

| 3.  | load                  |                                                            | $\rho[x \leftarrow \cup_{\forall o \in \rho(y)} \sigma(o, f)]$                   |

| 4a. | store (strong update) |                                                            | $\forall o \in \rho(x), \ \sigma[(o, f) \leftarrow \rho(y)]$                     |

| 4b  | store (weak update)   |                                                            | $\forall a \in \rho(x), \ \sigma[(o, f) \leftarrow \sigma(a, f) \vdash \rho(y)]$ |

| 4b. | store (weak update)   | x.f = y                                                    | $\forall o \in \rho(x), \ \sigma[(o,f) \leftarrow \sigma(o,f) \cup \rho(y)]$     |

- Intra-procedural analysis:

- Analyze each procedure independently.

- At a call-site assume the worst-case scenario.

- Constant propagation?

- Points-to Analysis?

- Inter-procedural analysis:

- Analyze the whole program, while being aware of the procedure details.

CS6235 - Jan 2023

• Need to know about who-calls-whom? - Call Graph.

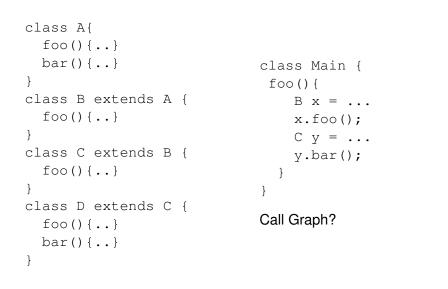

### Call Graph Construction

- Call Graph G = (N, S, E, r).

- *N* = set of all the functions.

- $r \in N$  is the root (main method).

- S = set of call site labels (for example, line numbers).

- $\forall n_1, n_2 \in N$ , we say  $(n_1, s, n_2) \in E$ ) if  $n_1$  may call  $n_2$  at call site s.

- In a function  $n_1$ , if there exists a call of the form x.foo(), then the edges to add: From  $n_1$  to

- every foo in the program (too conservative).

- $\bullet\,$  every foo present in the possible classes whose object x may contain.

- Decide this list just based on the class hierarchy (CHA).

- Decide this list by doing a flow analysis (CFA not covered).

CS6235 - Jan 2023

```

106/234

```

V.Krishna Nandivada (IIT Madras)

### **Class Hierarchy Analysis**

### Dimensions of Analysis

- Context insensitive (call site independent).

- For each procedure in a program identify the subset of its parameters, such that each of the parameters will get a single "value", across all the invocations.

- The procedure will return a single "value" across all the invocations.

- Context sensitive (call site dependent):

- for each particular procedure called from a particular context (a particular site), the subset of parameters that have the same "value" each time the procedure is called at that site.

- For each call site, the function may return a different "value".

What are the "values"? Depends on the analysis.

### Context-insensitive points-to analysis

| 1 <b>F</b> | Function InterProcPointsTo(CallGraph CG)                                          |  |  |  |

|------------|-----------------------------------------------------------------------------------|--|--|--|

| 2 W        | worklist = {CG.root};                                                             |  |  |  |

| 3 <b>V</b> | hile worklist is not empty do                                                     |  |  |  |

| 4          | p = worklist.dequeue();                                                           |  |  |  |

| 5          | begin                                                                             |  |  |  |

| 6          | Process stmts in p like before; // Intra-procedural analysis till fixed-point     |  |  |  |

| 7          | During the analysis, if we encounter a stmt s of the form $x=y.foo()$             |  |  |  |

|            | then                                                                              |  |  |  |

| 8          | compute the actual arguments of <i>s</i> ;                                        |  |  |  |

| 9          | foreach function $q$ that may be called at $s$ do                                 |  |  |  |

| 10         | Compute <i>meet</i> : current values for the formals of <i>q</i> and the actuals; |  |  |  |

| 11         | if the values of the arguments of $q$ have changed then                           |  |  |  |

| 12         | remember the new value and add q to the worklist;                                 |  |  |  |

| 13         | "Update" the value of x and all the fields of the arguments to $f_{00}$           |  |  |  |

| 15         | as per the summary of $q$ .                                                       |  |  |  |

|            |                                                                                   |  |  |  |

| 14         | v =  compute the meet of all the return values of $p$ ;                           |  |  |  |

| 15         | Set the return value of $p$ to $v$ ;                                              |  |  |  |

| 16         | Set the summary of $p$ to include the final values of the formal arguments;       |  |  |  |

| 17         |                                                                                   |  |  |  |

| 19         |                                                                                   |  |  |  |

|            | V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023 109/234                        |  |  |  |

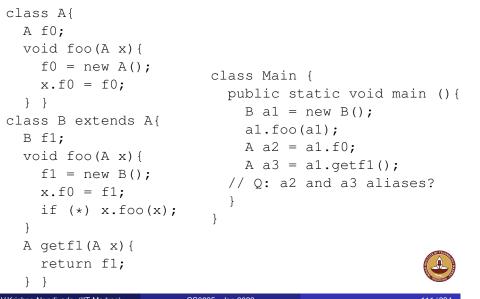

### Example II/II (Impact of imprecise call-graph)

### Example I/II

```

class A{

A f0;

class Main {

void foo(A x) {

public static void main () {

f0 = new A();

B a1 = new B();

x.f0 = f0;

a1.foo(a1);

} }

A = a1.f0;

class B extends A{

A = a1.getf1();

B f1;

// Q: a2 and a3 aliases?

void foo(A x) {

a2.foo(a3);

f1 = new B();

A = a2.f0;

x.f0 = f1;

// Q: a2 and a4 aliases?

}

}

A getf1(){

}

return f1;

} }

```

```

V.Krishna Nandivada (IIT Madras)

```

```

CS6235 - Jan 2023

```

```

110/234

```

### **Escape Analysis**

### on board.

V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023 113/234

# Symbol table information

A compiler uses symbol table to store many different types of information.

What kind of information might the compiler need?

- textual name

- data type

- dimension information

- declaring procedure

- lexical level of declaration

- storage class

- offset in storage

- if record, pointer to structure table

- if parameter, by-reference or by-value?

- can it be aliased? to what other names?

- number and type of arguments to functions

- ...

### (for aggregates)

### (base address)

### Outline

### Introduction

### 2 Program Analysis Basics

### 3 Symbol Tables and Intermediate Representation

- Symbol Tables

- Intermediate Representation

- 4 Data Race Detection

- Deadlock Analysis

- Memory consistency models

# V.Krishna Nandivada (IIT Madras) CS6235 - Jan 2023

114/234

### Symbol table organization

How should the table be organized?

- Linear List

- **O**(*n*) probes per lookup

- easy to expand no fixed size

- one allocation per insertion

- Ordered Linear List

- $O(\log_2 n)$  probes per lookup using binary search

- insertion is expensive (to reorganize list)

- Binary Tree

- **O**(*n*) probes per lookup unbalanced

- **O**(log<sub>2</sub> n) probes per lookup balanced

- easy to expand no fixed size

- one allocation per insertion

- Hash Table

- **O**(1) probes per lookup on average

- expansion costs vary with specific scheme

### Nested scopes: block-structured symbol tables

What information is needed?

- when asking about a name, want most recent declaration

- declaration may be from current scope or outer scope

- innermost scope overrides outer scope declarations

Key point: new declarations occur only in current scope What operations do we need?

- void put (Symbol key, Object value) bind key to value

- Object get(Symbol key) return value bound to key

- void beginScope() remember current state of table

- void endScope()

close current scope and restore table to state at most recent open beginScope

```

V.Krishna Nandivada (IIT Madras)

```

CS6235 - Jan 2023

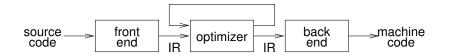

### Intermediate representations

# Why use an intermediate representation? Intermediate representation? Intermediate representation? Intermediate compiler into manageable pieces good software engineering technique simplifies retargeting to new host isolates back end from front end simplifies handling of "poly-architecture" problem m lang's, n targets ⇒ m+n components Intermediate representation is a compile-time data structure

### Attribute information

Attributes are internal representation of declarations Symbol table associates names with attributes Names may have different attributes depending on their meaning:

- variables: type, procedure level, frame offset

- types: type descriptor, data size/alignment

- constants: type, value

- procedures: formals (names/types), result type, block information (local decls.), frame size

CS6235 - Jan 2023

### Intermediate representations

Generally speaking:

- front end produces IR

- optimizer transforms that representation into an equivalent program that may run more efficiently

- back end transforms IR into native code for the target machine

(myth)

### Intermediate representations

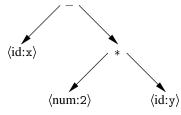

### Representations talked about in the literature include:

- abstract syntax trees (AST)

- linear (operator) form of tree

- directed acyclic graphs (DAG)

- control flow graphs

- program dependence graphs

- static single assignment form

- 3-address code

- hybrid combinations

- Parallel Program Graphs

- Program Structure Tree/Graphs

- Concurrent Control Flow Graphs

- ...

V.Krishna Nandivada (IIT Madras)

CS6235 - Jan 2023

### IR design issues

- Is the chosen IR appropriate for the (analysis/ optimization/ transformation) passes under consideration?

- What is the IR level: close to language/machine.

- Multiple IRs in a compiler: for example, High, Medium and Low

$\begin{array}{c} x = a[i,j+2] \\ x = a[i,j+2] \\ & t1 = j + 2 \\ t2 = i * 20 \\ t3 = t1 + t2 \\ t4 = 4 * t3 \\ t5 = addr a \\ t6 = t5 + t4 \\ x = *t6 \\ \end{array} \begin{array}{c} r1 = [fp-4] // j \\ r2 = r1 + 2 \\ r3 = [fp-8] // i \\ r4 = r3 * 20 \\ r5 = r4 + r2 \\ r6 = 4 * r5 \\ r7 = fp - 216 // a \\ x = [r7+r6] \end{array}$

• In reality, the variables etc are also only pointers to other data structures.

### Important IR Properties

- ease of generation

- ease of manipulation

- cost of manipulation

- level of abstraction