# On Syntactic Multilinear Arithmetic Circuits\*

Maurice Jansen<sup> $\dagger$ </sup>

Institute for Theoretical Computer Science, Tsinghua University, Beijing - 100084, China. maurice.julien.jansen@gmail.com Meena Mahajan

The Institute of Mathematical Sciences, Chennai 600113, India meena@imsc.res.in

B. V. Raghavendra  $\operatorname{Rao}^{\ddagger}$

Universität des Saarlandes, Informatik 66041 Saarbrücken, Germany bvrr@cs.uni-sb.de

November 16, 2010

#### Abstract

The class of polynomials computable by polynomial size arithmetic log depth circuits  $(VNC^1)$  is known to have equivalent constant width polynomial degree circuits  $(VsSC^0)$ , but the converse containment is unknown. In a partial answer to this question, we show that syntactic multilinear circuits of constant width and polynomial degree can be depth-reduced *i.e.* sm-VsSC<sup>0</sup>  $\subseteq$  sm-VNC<sup>1</sup>. Further, we give a width-efficient simulation for constant width syntactic multilinear circuits by constant width syntactic multilinear algebraic branching programs *i.e.* sm-VsSC<sup>0</sup>  $\subseteq$  sm-VBWBP.

We then focus on polynomial-size syntactic multilinear circuits, and study relationships between classes of functions obtained by imposing various resource (width, depth, degree) restrictions on these circuits. Along the way we also observe a characterization of the class  $NC^1$  in terms of a restricted class of planar branching programs of polynomial size.

Finally, in sharp contrast to the general case, we report closure and stability of coefficient functions for the syntactic multilinear classes studied in the paper.

<sup>\*</sup>The results in this paper were announced in MFCS 2008 and CSR 2009, in [MR08, JR09].

<sup>&</sup>lt;sup>†</sup>This work was done when this author was employed at Aarhus University.

<sup>&</sup>lt;sup>‡</sup>This work was done when this author was at the Institute of Mathematical Sciences, Chennai.

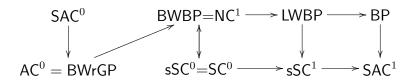

Figure 1: Boolean complexity classes around  $NC^1$ . Arrow  $(\rightarrow)$  indicates containment.

## 1 Introduction

The class  $NC^1$  of Boolean functions computed by logarithmic depth polynomial size circuits has several equivalent characterisations, in the form of polynomial size bounded width branching programs (BWBP), polynomial size formulas (F), and bounded width circuits of polynomial size ( $SC^0$ ) *i.e.*  $NC^1 = BWBP = F = SC^0$ . Its subclass  $AC^0$ , consisting of Boolean functions computed by polynomial size constant depth unbounded fan-in circuits, has also been characterised via restricted branching programs (BWrGP). See Figure 1. However, the counting and arithmetic versions of those classes which are equivalent to  $NC^1$  seem to represent different classes of functions. In [CMTV98], it was shown that if inputs take the values from  $\{0, 1\}$ , then the class of functions represented as the total weights of paths in a constant width branching program with edge weights from  $\{x_1, \ldots, x_n, -1, 0, 1\}$  coincide with the class functions computable by polynomial size and log-depth arithmetic circuits over  $\{+, \times, -1, 0, 1, x_1, \ldots, x_n\}$ , *i.e.* GapBWBP = GapNC<sup>1</sup>. In [LMR10], this study was extended to bounded width circuits of small (polynomial) degree and size, *i.e.* sSC<sup>0</sup>, showing that GapNC<sup>1</sup>  $\subseteq$  GapsSC<sup>0</sup>, but it is not known whether this containment is strict or not.

The question  $\mathsf{GapsSC}^0 \subseteq \mathsf{GapNC}^1$  can be seen as a depth reduction problem for bounded width circuits. In the algebraic model introduced by Valiant (see [Val82, Bür00]), where arbitrary constants from the underlying field are allowed, this question can be re-stated as: is the class of constant width polynomial size arithmetic circuits of polynomial syntactic degree (VsSC<sup>0</sup>) contained in the class of polynomial size arithmetic formulas? *i.e.* is VsSC<sup>0</sup>  $\subseteq$  VNC<sup>1</sup>? (We use the prefix V to denote Valiant's model.) An ideal result would be a bounded width version of the depth reduction given in [VSBR83], *i.e.* the resulting circuit needs to have + fan-in bounded by a function of the width of the original circuit. But it is not clear how this can be achieved. So, one of the natural ways to proceed is to look for restrictions on the circuits where this can be achieved. The main focus of this paper is the restriction of syntactic multilinearity on the arithmetic circuits and branching programs. We show that the classes VsSC<sup>0</sup>, VNC<sup>1</sup> and VBWBP behave very differently in the syntactic multilinear world.

In a multilinear arithmetic is circuit every gate computes a multilinear polynomial. Syntactic multilinearity (sm for short) is further a restriction on the syntactic structure of a multilinear arithmetic circuit, it was introduced by Ran Raz in [Raz04a]. In a syntactic multilinear circuit, every multiplication gate operates on disjoint sets of variables. (A formal definition is given in Section 2.) In [Raz04a], Ran Raz proved super polynomial lower bounds for multilinear arithmetic formula computing the permanent or determinant. The argument in [Raz04a] is against syntactic multilinear arithmetic formula and then uses the equivalence of the two notions for arithmetic formulas. Later in [Raz04b], it was shown that the multilinear versions of the classes  $VNC^1$  and  $VNC^2$  are different. In [RY08a], the depth reduction technique of [VSBR83] was shown to be preserving the property of syntactic multilinearity. In [RSY08] an explicit polynomial is shown to require a size of  $\Omega(n^{4/1}/\log^2 n)$  for any syntactic multilinear arithmetic circuit computing it. In [RY08b], explicit lower bounds against noise-resistant, non-cancelling and orthogonal syntactic multilinear arithmetic circuits were given.

Motivated by the above series of papers, we explore the question  $VsSC^0 \stackrel{?}{\subseteq} VNC^1$  through the lens of syntactic multilinearity.

Firstly, we give a depth reduction for constant width syntactic multilinear arithmetic circuits. We show that a syntactic multilinear circuit of constant width and polynomial size has an equivalent syntactic multilinear formula of logarithmic depth and polynomial size (Theorem 3 and Corollary 4). Thus, if restricted to be syntactic multilinear, then the class  $VNC^1$  is at least as powerful as  $VsSC^0$ . (Note that log depth formulas give exactly  $VNC^1$  even in the syntactic multilinear world.). But ironically, the containment  $VNC^1 \subseteq VsSC^0$  does not seem to translate into the syntactic multilinear world. This is mainly because the only known translation ([BC92]) from a log-depth formula into a constant width branching program (and hence an  $sSC^0$  circuit) does not preserve syntactic multilinearity.

Now the scenario is :  $sm-VBWBP \subseteq sm-VsSC^0 \subseteq sm-VNC^1$ . (The sm- prefix denotes the restriction to syntactic multilinear circuits.) Looking to tighten this relationship, we obtain a somewhat surprising result: syntactic multilinear algebraic branching programs of constant width and polynomial size are as powerful as syntactic multilinear circuits of constant width and polynomial size (Theorem 9). Thus the restriction of syntactic multilinearity pulls  $VsSC^0$  down to VBWBP. In order to establish this, we use the equivalence of skew circuits and branching programs, and the notions of weakly skew circuits, first studied in the context of Boolean circuits in [Tod92], and multiplicatively disjoint circuits, introduced in [MP08].

The two results described above give a reversal in the relationships among the three classes VBWBP, VNC<sup>1</sup> and VsSC<sup>0</sup>: In the general world, VsSC<sup>0</sup> is the strongest class and the other two are equal and contained in VsSC<sup>0</sup>, *i.e.* VBWBP = VNC<sup>1</sup>  $\subseteq$  VsSC<sup>0</sup>. In the syntactic multilinear world, sm-VNC<sup>1</sup> turns out to be the strongest class, whereas the other two are equal and contained in it, *i.e.* sm-VBWBP = sm-VsSC<sup>0</sup>  $\subseteq$  sm-VNC<sup>1</sup>. This indicates that standard simulations may fail in the syntactic multilinear world, and need to be examined afresh. We do this next, showing that the classic depth-reduction of [Bre73] works in this setting (Theorem 20), as also the divide-and-conquer technique of Savitch converting branching programs to circuits (Lemma 21), and the folklore staggering (see [IZ94]) of a small-depth to a small-width circuit (Lemma 22). A more recent characterisation of arithmetic AC<sup>0</sup> via restricted planar branching programs, [AAB+99], also carries through (Corollary 26). In fact, examining this more closely, we obtain a characterisation of Boolean NC<sup>1</sup> as well as VNC<sup>1</sup> via polynomial size branching programs of log width or unbounded width, with the same restricted planarity condition (Corollary 27).

Another context in which we study the effect of syntactic multilinearity is the complex-

ity of coefficient functions, first studied in a systematic way in [Mal07]. In general, these functions can be quite hard to compute. However for most syntactic multilinear classes, we show that the coefficient functions are also computable within the same class. Further, exponential sums are also computable within the respective classes. (Theorems 28,30)

The rest of the paper is organized as follows: In section 2 we give formal definitions of syntactic multilinear circuits. Section 3 contains a depth reduction for syntactic multilinear constant-width circuits. In section 4 we give a width preserving simulation of constant width syntactic multilinear circuits by syntactic multilinear algebraic branching programs. In Section 5 we discuss the relationships among syntactic multilinear classes. In Section 6 we discuss the coefficient functions for syntactical multilinear classes.

## 2 Preliminaries

#### 2.1 Arithmetic Circuits and Algebraic Branching Programs

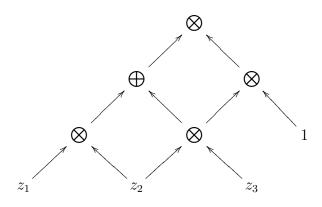

Let  $\mathbb{K}$  be a fixed ring or a field. Let  $X = \{x_1, \ldots, x_n\}$  be variables that take values from  $\mathbb{K}$ . An arithmetic circuit (or a straight line program) over  $\mathbb{K}$  is a directed acyclic multigraph C, where nodes of zero in-degree are called input gates and are labeled from the set  $\mathbb{K} \cup \{x_1, \ldots, x_n\}$ . The nodes of zero out-degree are called output gates. The remaining nodes of C are labeled from  $\{+, \times\}$ . Whenever not stated explicitly, we assume that in-degree of every node is bounded by 2. A gate f computes a polynomial  $p_f$  in  $\mathbb{K}[X]$  which can be defined inductively in a natural way: an input gate computes a polynomial that is a constant or a single-variable monomial; if  $f = g \times h$ , then  $p_f = p_g \times p_h$ , where  $p_g$  and  $p_h$  are polynomials computed by g and h respectively (available by induction); and if f = g+h, then  $p_f = p_g+p_h$ . The set of polynomials computed at its output gates constitute the polynomials computed by a circuit. In what follows, we may use the same symbol f for representing both the gate and the polynomial represented by it. A polynomial family  $(f_n)_{n\geq 0}$  is said to be computed by a circuit family  $(C_n)_{n\geq 0}$  if  $\forall n \geq 0$ ,  $f_n$  is computed by  $C_n$ .

Without loss of generality, we assume that a circuit is layered, *i.e.* there is partition  $V_1, \ldots, V_\ell$  of the non-input gates in the circuits so that all in-coming edges of  $V_i$  are either from input-gates or from  $V_{i-1}$ ,  $1 < i \leq \ell$ . The measures of size, depth, width and syntactic degree of a circuit is defined in the same way as in the case of Boolean circuits: size is the number of gates, depth is the length of the longest path from a leaf gate to an output gate, width is the maximum number of gates per layer in a layered circuit where all edges are from a layer to the next, and the syntactic degree d(f) of a gate f is inductively defined to be 1 at an input gate,  $\max\{d(g), d(h)\}$  if f = g + h, and d(g) + d(h) if  $f = g \times h$ .

A formula is a circuit where out-degree of every gate is bounded by 1. A skew arithmetic circuit is a circuit in which for every gate  $f = g \times h$ , either  $g \in \mathbb{K} \cup X$  or  $h \in \mathbb{K} \cup X$  or both.

An algebraic branching program (ABP) over a field  $\mathbb{K}$  is a layered directed acyclic graph G with two designated nodes s (of zero in-degree) and t (of zero out-degree), in which the edges are labeled from  $\mathbb{K} \cup X$ , where  $X = \{x_1, \ldots, x_n\}$ . For any s-t path P in G, weight(P) is defined to be the product of the labels of edges that appear in P. The polynomial  $f_G$

Figure 2: The possible patterns between two layers of rGPs. Edges without any label are of weight 1 and  $c \in X \cup \mathbb{K}$

computed by G is defined as  $\sum_{P} \text{weight}(P)$ , where P ranges over all s-t paths in G. The size of an ABP is the number of nodes in it. Width is the maximum number of nodes at any layer. Length of an ABP is the total number of layers in it. In this paper, we assume (without loss of generality) that the in and out-degrees of every node in the ABP is bounded by a constant.

As in the case of Boolean and counting circuits, a *skew* arithmetic circuit can be transformed into an algebraic branching program and vice versa. (See [Nis91].) In fact this transformation increases the width and size by only a constant factor.

*G*-graphs are graphs that have planar embeddings where vertices are embedded on a rectangular grid, and all edges are between adjacent columns from left to right. In these graphs, the node *s* is fixed as the leftmost bottom node and *t* is the rightmost top node. In [AAB<sup>+</sup>99], a restriction of *G*-graphs is considered where the width of the grid is a constant, and only certain kinds of connections are allowed between any two layers. Namely, for width 2k + 2, the connecting pattern at any layer is represented by one of the graphs  $G_{k,i}$  (see figure 2) for  $0 \le i \le 2k + 2$ . An rGP (short for restricted grid branching program) is an algebraic branching program where the underlying graph is a restricted *G*-graph of the aforementioned form.

#### 2.2Valiant's Classes

.

In Valiant's model, a complexity class is a set of families of polynomials  $f = (f_n)_{n \ge 0}$ , where  $f_n \in \mathbb{K}[X_1, \ldots, X_n]$ . In this paper, the prefix V denotes an algebraic class in this model. We now define the different complexity classes that are studied in this model. For all the classes, we assume that polynomials have degree bounded by poly(n).

#### Definition 1

$$\begin{split} \mathsf{VP} &= \left\{ f = (f_n)_{n \geq 0} \mid \begin{array}{l} f_n \ can \ be \ computed \ by \ a \ polynomial \ size \ arithmatic \ metic \ circuit, \ and \ \deg(f_n) \leq \mathsf{poly}(n). \end{array} \right\} \\ \mathsf{VNP} &= \left\{ f = (f_n)_{n \geq 0} \mid \begin{array}{l} \exists \ a \ polynomial \ family \ g \ = \ (g_m)_{m \geq 0} \in \mathsf{VP} \\ such \ that \ f_n(X) = \sum_{e \in \{0,1\}^{m'}} g_{m'+n}(X,e), \ where \\ m', \ \deg(f_n) \leq \mathsf{poly}(n). \end{array} \right\} \\ \mathsf{VF} = \mathsf{VP}_e \ = \left\{ f = (f_n)_{n \geq 0} \mid \begin{array}{l} f \in \mathsf{VP}; \ and \ f_n \ can \ be \ computed \ by \ a \ polynomial \\ size \ arithmatic \ formula. \end{array} \right\} \\ \mathsf{VP}_{skew} \ = \left\{ f = (f_n)_{n \geq 0} \mid \begin{array}{l} f \in \mathsf{VP}; \ and \ f_n \ can \ be \ computed \ by \ a \ polynomial \\ size \ skew \ arithmatic \ circuit. \end{array} \right\} \\ \mathsf{VBP} \ = \left\{ f = (f_n)_{n \geq 0} \mid \begin{array}{l} f \in \mathsf{VP}; \ and \ f_n \ can \ be \ computed \ by \ a \ polynomial \\ size \ algebraic \ branching \ program \end{array} \right\} \\ \mathsf{VBP}[w] \ = \left\{ f = (f_n)_{n \geq 0} \mid \begin{array}{l} f_n \ can \ be \ computed \ by \ a \ polynomial \\ size \ algebraic \ branching \ program \ of \ width \ O(w) \end{array} \right\} \\ \mathsf{VLWBP} = \mathsf{VBP}[\log n] \ ; \ \mathsf{VBWBP} = \mathsf{VBP}[1] \end{split}$$

$$\mathsf{VNC}^{i} = \begin{cases} f \in \mathsf{VP}; \text{ and } f_{n} \text{ can be computed by polynomial} \\ f = (f_{n})_{n \geq 0} \mid \text{size } O(\log^{i} n) \text{ depth arithmetic circuits of constant fan-in} \end{cases}$$

$$\mathsf{VAC}^0 = \left\{ f = (f_n)_{n \ge 0} \mid \begin{array}{l} f \in \mathsf{VP}; \ and \ f_n \ can \ be \ computed \ by \ polynomial \\ size \ and \ constant \ depth \ arithmetic \ circuits \ with \\ unbounded \ fan-in \ gates \end{array} \right\}$$

$\mathsf{VSAC}^{i} = \left\{ f = (f_{n})_{n \geq 0} \mid \begin{array}{l} f \in \mathsf{VP}; \text{ and } f_{n} \text{ can be computed by polynomial} \\ size \ O(\log^{i} n) \text{ depth arithmetic circuits with con-} \\ stant \text{ fan-in for } \times \text{ gates and unbounded fan-in} \\ for + \text{ gates} \end{array} \right\}$

$$\mathsf{VLWF} = \left\{ f = (f_n)_{n \ge 0} \mid \begin{array}{c} f \in \mathsf{VP}; \text{ and } f_n \text{ can be computed by a polynomial} \\ \text{size arithmetic formula of } O(\log n) \text{ width} \end{array} \right\}$$

$$\mathsf{VrGP} = \left\{ f = (f_n)_{n \ge 0} \mid \begin{array}{c} f \in \mathsf{VP}; \text{ and } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f \in \mathsf{VP}; \text{ and } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f \in \mathsf{VP}; \text{ and } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f \in \mathsf{VP}; \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f \in \mathsf{VP}; \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f \in \mathsf{VP}; \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or } f_n \text{ can be computed by polynomial} \\ \text{vrGP} \text{ or }$$

$$/rGP = \left\{ f = (f_n)_{n \ge 0} \mid \begin{array}{c} f \in VP; and f_n \ can be computed by polynomial \\ size \ restricted \ grid \ algebraic \ branching \ program \end{array} \right\}$$

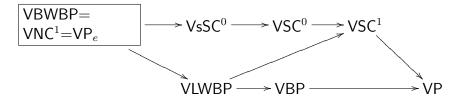

Figure 3: Relationships among complexity classes in Valiant's model

$$\begin{aligned} \mathsf{VBWrGP} &= \left\{ f = (f_n)_{n \ge 0} & | \begin{array}{c} f \in \mathsf{VP}; \ and \ f_n \ can \ be \ computed \ by \ polynomial \\ size \ restricted \ grid \ algebraic \ branching \ program \\ of \ constant \ width \end{aligned} \right\} \\ \mathsf{VsSC}^i &= \left\{ f = (f_n)_{n \ge 0} \ | \begin{array}{c} f_n \ can \ be \ computed \ by \ an \ arithmetic \ circuit \ of \\ polynomial \ size \ and \ polynomial \ syntactic \ degree, \\ and \ width \ O(\log^i n). \end{array} \right\} \\ \mathsf{VSC}^i &= \left\{ f = (f_n)_{n \ge 0} \ | \begin{array}{c} f_n \ can \ be \ computed \ by \ a \ polynomial \ syntactic \ degree, \\ and \ width \ O(\log^i n). \end{array} \right\} \\ \mathsf{VSC}^i &= \left\{ f = (f_n)_{n \ge 0} \ | \begin{array}{c} f_n \ can \ be \ computed \ by \ a \ polynomial \ size \ circuit \ of \\ width \ O(\log^i n), \ and \ \deg(f_n) \le \mathsf{poly}(n) \end{array} \right\} \end{aligned}$$

Figure 3 shows the known relationships among some of the classes defined above.

#### 2.3 Syntactic Multilinear Circuits

We now define multilinear and syntactic multilinear circuits, following notation from [Raz04a]. We call a polynomial p multilinear, if for any monomial of p the individual degree of every variable is bounded by one. Let C be an arithmetic circuit over the ring  $\mathbb{K}$ , and let  $X = \{x_1, \ldots, x_n\}$  be its input variables. For a gate g in C, let  $p_g \in \mathbb{K}[X]$  be the polynomial computed at g. Let  $X_g \subseteq X$  denote the set of variables that occur in the sub-circuit rooted at g. C is called multilinear if for every gate  $g \in C$ ,  $p_g$  is a multilinear polynomial. C is said to be syntactic multilinear if for every multiplication gate  $g = h \times f$  in C,  $X_h \cap X_f = \emptyset$ .

In the case of formulas, the notion of multilinearity and syntactic multilinearity are (nonuniformly) equivalent ([RY08a]).

In the case of algebraic branching programs, the notion of syntactic multilinearity coincides with the read-once property, where no variable appears more than once on any path. (See [BRS93] for more about Boolean read once branching programs). Namely, we say an algebraic branching program P is multilinear if for every node v in P, the polynomial  $p_v$ (sum of weights of all *s*-v paths ) is multilinear. Furthermore, P is defined to be syntactic multilinear if in every path of the program (not just *s*-to-*t* paths), no variable appears more than once; *i.e.* the algebraic branching program is syntactic read-once.

For any algebraic complexity class VC, we denote by m-VC and sm-VC respectively the functions computed by multilinear and syntactic multilinear versions of VC.

In [RY08a] it is shown that the depth reduction of [VSBR83] preserves syntactic multilinearity; thus **Proposition 2** ([**RY08a**]) Any function computed by a syntactic multilinear polynomial size polynomial degree arithmetic circuit is in  $sm-VSAC^1$ .

## 3 Depth Reduction in Small Width sm-Circuits

This entire section is devoted to a proof of Theorem 3 below, which says that a circuit width bound can be translated to a circuit depth bound, provided the given small-width circuit is syntactic multilinear.

**Theorem 3** Let C be a syntactic multilinear arithmetic circuit of depth l and width w and syntactic degree d, with  $X = \{x_1, \ldots, x_n\}$  as the input variables, and constants from the ring K. Then, there is a syntactic multilinear circuit E of depth  $O(w^2 \log l + \log d)$  and size  $O(2^{w^2}l^{25w^2} + 4lwd)$  computing the same polynomial as C.

An immediate corollary is,

Corollary 4 sm-VsSC<sup>0</sup>  $\subseteq$  sm-VNC<sup>1</sup>.

It can also be seen that if we apply Theorem 3 to a syntactic multilinear arithmetic circuit of poly-logarithmic width and quasi-polynomial size and degree, then we get a poly-logarithmic depth circuit of quasi-polynomial size. Thus

**Corollary 5**

sm-Size, Width,  $Deg(2^{poly(log)}, poly(log), 2^{poly(log)})$  $\subseteq$  sm-Size, Width,  $Depth(2^{poly(log)}, poly, poly(log))$

where sm-Size, Width, Deg(s, w, d) is the class of polynomials computable by syntactic multilinear circuit of size s, width w and depth d.

We first give a brief outline of the technique used. We actually show something stronger: not only can we evaluate the polynomials computed at the output level, but also, if we express these polynomials as polynomials exclusively in the variables at the lowest level, then we can evaluate all coefficients of the new polynomials in small depth. Note that the coefficients may not be ring elements but are themselves polynomials in the remaining variables.

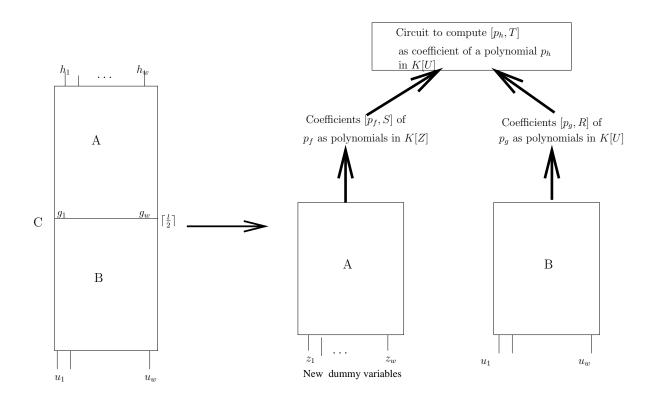

To show this stronger claim, we cut the circuit C at length  $\lceil \frac{l}{2} \rceil$ , to obtain circuits A (the upper part) and B (the lower part). Let  $M = \{g_1, \ldots, g_w\}$  be the gates of C at level  $\lceil \frac{l}{2} \rceil$ . A is obtained from C by replacing the gates in M by a set  $Z = \{z_1, \ldots, z_w\}$  of new variables. Each gate g of A (or B) represents a polynomial  $p_g \in \mathbb{K}[X, Z]$ , and can also be viewed as a polynomial in K[Z], where  $K = \mathbb{K}[X]$ . Since A and B are circuits of length bounded by  $\lceil \frac{l}{2} \rceil$ , we use induction on each of them. Now we need additional circuitry to patch together the coefficients so computed and obtain the coefficients corresponding to C. See Figure 4.

For this approach to work, we need to eliminate constants, since they may violate syntactic multilinearity if replaced by variables at the slice layer. We say that a gate syntactically computes a constant if each leaf descendant of the gate is labelled by a constant. Without

Figure 4: Breaking up circuit C into A and B

loss of generality, we can assume that in the circuit C, no gate syntactically computes a constant. If there is such a gate, simply replace it by a leaf with the computed constant. This is a non-uniform step. Alternatively, to preserve uniformity, identify the gates that syntactically compute constants, label all outgoing wires of these gates by new variables from a set Y, and proceed with this new circuit. It is easy to see that the new circuit is syntactic multilinear in  $X \cup Y$ .

To simplify the following construction, we explicitly relabel each leaf labeled by a constant with a new variable from a set Y.

We now show, in Lemma 6, how to achieve depth reduction for syntactic multilinear bounded width circuits which have no constants. This completes the proof of Theorem 3 as well; all we need to do is to explicitly plug in the constants corresponding to the variables in Y

**Lemma 6** Let C' be a width w, length l syntactic multilinear arithmetic circuit with leaves labeled from  $X \cup Y$  (no constants). Then there is an equivalent syntactic multilinear arithmetic formula C'' of size  $O(2^{w^2}l^{25w^2})$  and depth  $O(w^2 \log l)$  which computes the same polynomial as C'.

To establish lemma 6, we use the intuitive idea sketched earlier; slice the circuit horizontally, introduce dummy variables along the slice, and proceed inductively on each part. Now the top part has three types of variables: circuit inputs X, variables representing constants Y, and variables along the slice Z. The variables Z appear only at the lowest level of the upper half of the circuit. Note that this circuit for the top part is syntactic multilinear in Zas well.

To complete an inductive proof for Lemma 6, we need to show depth-reduction for such circuits. We use Lemma 7 below, which tells us that viewing each gate as computing a polynomial in Z, with coefficients from  $K = \mathbb{K}[X, Y]$ , there are small-depth circuits representing each of the coefficients. We then combine these circuits to evaluate the original circuit.

More formally, let D be a width w, depth l, syntactic multilinear circuit, with all leaves labeled from  $X \cup Y \cup Z$  (no constants), where variables from  $Z = \{z_1, \ldots, z_w\}$  appear only at the lowest level of the circuit. Let  $h_1, \ldots, h_w$  be the set of output gates of D *i.e.* gates at level l. Let  $p_{h_i} \in \mathbb{K}[X, Y, Z]$  denote the multilinear polynomial computed at  $h_i$ . Note that  $p_{h_i}$  can also be viewed as a polynomial in K[Z], *i.e.* a multilinear polynomial with variables from Z and polynomials from  $\mathbb{K}[X, Y]$  as its coefficients; we use this viewpoint below. For  $T \subseteq \{1, \ldots, w\}$ , let  $[p_{h_i}, T] \in \mathbb{K}[X, Y]$  denote the coefficient of the monomial  $m_T = \prod_{j \in T} z_j$ in  $p_{h_i}$ . The following lemma tells us how to evaluate these coefficients  $[p_{h_i}, T]$ .

**Lemma 7** With circuit D as above,  $\forall h \in \{h_1, \ldots, h_w\}$  and  $T \subseteq \{1, \ldots, w\}$ , there is a bounded fan-in syntactic multilinear arithmetic formula  $D^{h,T}$  of size bounded by  $2^{w^2}l^{25w^2}$  and depth  $O(w^2 \log l)$ , with leaves labeled from  $X \cup Y \cup \{0,1\}$ , such that the value computed at its output gate is exactly the coefficient  $[p_h, T]$ .

**Proof:** We proceed by induction on the depth l of the circuit.

Basis : l = 1. Different possibilities are as follows.

$$\begin{array}{ll} h = z_i z_j : & [p_h, T] = 1 \text{ for } T = \{i, j\} \text{ and } 0 \text{ otherwise.} \\ h = a z_i : & [p_h, T] = a \text{ for } T = \{i\} \text{ and } 0 \text{ otherwise.} \\ h = a : & [p_h, T] = a \text{ for } T = \emptyset \text{ and } 0 \text{ otherwise.} \\ h = z_i + z_j : & [p_h, T] = 1 \text{ for } T = \{i\} \text{ or } T = \{j\} \text{ and } 0 \text{ otherwise.} \\ h = a + z_i : & [p_h, \emptyset] = a, [p_h, \{i\}] = 1, \text{ and } [p_h, T] = 0 \text{ otherwise.} \\ \end{array}$$

Where  $a \in X \cup Y \cup \mathbb{K}$ .

Hypothesis: Assume that the lemma holds for all circuits D' of depth l' < l and width w.

Induction Step: Let D be the given circuit of depth l, syntactic multilinear in  $X \cup Y \cup Z$ , where variables from Z appear only at the lowest level of D. Let  $\{h_1, \ldots, h_w\}$  be the output gates of D. Let  $\{g_1, \ldots, g_w\}$  be the gates of D at level  $l' = \lceil \frac{l}{2} \rceil$ . Denote by A the circuit resulting from replacing gates  $g_i$  with new variables  $z'_i$  for  $1 \leq i \leq w$ , and removing all the gates below level l', and denote by B the circuit with  $\{g_1, \ldots, g_w\}$  as output gates, *i.e.* gates above the  $g_i$ 's are removed. We rename the output gates of A as  $\{f_1, \ldots, f_w\}$ . Let  $Z' = \{z'_1, \ldots, z'_w\}$ . Both A and B are syntactic multilinear circuits of depth bounded by l'and width w, and of a form where the inductive hypothesis is applicable. For  $i \in \{1, \ldots, w\}$ ,  $p_{f_i}$  is a polynomial in K[Z'] and  $p_{g_i}$  is a polynomial in K[Z], where  $K = \mathbb{K}[X, Y]$ .

Applying induction on A and B, for all  $S, Q \subseteq \{1, \ldots, w\}$ ,  $[p_{f_i}, S]$  and  $[p_{g_i}, Q]$  have syntactic multilinear arithmetic circuits  $A^{f_i,S}$  and  $B^{g_i,Q}$  respectively of size  $2^{w^2}(\lceil l/2 \rceil)^{25w^2}$  and depth  $w^2 \log(\lceil l/2 \rceil)$ . Note that  $p_{h_i}(Z) = p_{f_i}(p_{g_1}(Z), \ldots, p_{g_w}(Z))$ . But due to multilinearity,

$$p_{f_i}(Z') = \sum_{S \subseteq [w]} \left( [p_{f_i}, S] \prod_{s \in S} z'_s \right) \qquad \qquad p_{g_j}(Z) = \sum_{Q \subseteq [w]} \left( [p_{g_j}, Q] \prod_{q \in Q} z_q \right)$$

Using this expression for  $p_{f_i}$  in the formulation for  $p_{h_i}$ , we have

$$p_{h_i}(Z) = \sum_{S \subseteq [w]} \left( [p_{f_i}, S] \prod_{s \in S} p_{g_s}(Z) \right)$$

Hence, we can extract coefficients of  $p_{h_i}$  as follows. For any  $T \subseteq [w]$ , the coefficient of the monomial  $m_T$  in  $p_{h_i}$  is given by

$$[p_{h_i}, T] = \sum_{S \subseteq [w]} [p_{f_i}, S] \left( \text{ coefficient of } m_T \text{ in } \prod_{s \in S} p_{g_s}(Z) \right)$$

If S has t elements, then the monomial  $m_T$  is built up in t disjoint parts (not necessarily nonempty), where the kth part is contributed by the kth polynomial  $p_g$  in the above expression. So the coefficient of  $m_T$  is the product of the corresponding coefficients. Hence

$$[p_{h_i}, T] = \sum_{\substack{S = \{s_1, \dots, s_t\} \subseteq [w]}} \left( \begin{bmatrix} p_{f_i}, S \end{bmatrix} \sum_{\substack{Q_1, \dots, Q_t : \\ \text{partition of } T}} \prod_{k=1}^t [p_{g_{s_k}}, Q_k] \right)$$

(1)

We use this expression to compute  $[p_{h_i}, T]$ . We first compute  $[p_{f_i}, S]$  and  $[p_{g_j}, Q]$  for all  $i, j \in [w]$  and all  $S, Q \subseteq [w]$  using the inductively constructed sub-circuits. Then a circuit on top of these does the required combination. Since the number of partitions of T is bounded by  $w^w$ , while the number of sets S is  $2^w$ , this additional circuitry has size at most  $w^2 2^w w^w \leq 2^{w^2}$  (for  $w \geq 2$ ) and depth  $w \log w + w + \log w = O(w^2)$ .

**Preserving Syntactic Multilinearity:** Clearly, the circuit obtained above need not be syntactic multilinear. To achieve this, we do the following modifications:

- Unwind the expression for each  $[p_{h_i}, T]$  into a formula, by creating necessary copies of  $[p_{f_i}, S]$  and  $[p_{g_i}, Q]$  for all  $S, T, Q \subseteq \{1, \ldots, w\}$ .

- Consider a term  $[p_{f_i}, S][p_{g_1}, Q_1] \cdots [p_{g_t}, Q_t]$  which violates syntactic multilinearity. There are two cases:

- For some  $a \neq b$ ,  $[p_{g_a}, Q_a]$  and  $[p_{g_b}, Q_b]$  share a variable. If the corresponding term  $[p_{f_i}, S][p_{g_1}, Q_1] \cdots [p_{g_t}, Q_t]$  does not have any contribution to  $[p_{h_i}, T]$ , otherwise the original syntactic multilinear circuit C will have a  $\times$ -gate v such that the gates  $g_a$  and  $g_b$  are reachable via two different input gates of v, hence violating the syntactic multilinearity property. So this particular term  $[p_{f_i}, S][p_{g_1}, Q_1] \cdots [p_{g_t}, Q_t]$  can be replaced by 0 without changing the output.

- For some  $a \in S$ , sub-formulas  $[p_{g_a}, Q_a]$  and  $[p_{f_i}, S]$  share a variable, say x. At least one of the polynomials  $[p_{g_a}, Q_a]$  and  $[p_{f_i}, S]$  does not depend on x, since otherwise there is a gate v reachable from  $g_a$  in C violating the assumption of syntactic multilinearity of C. Now replace x with 0 in the corresponding sub-formula that does not depend on x.

Note that in the above process, we need to unwind the resulting circuit into a formula. By equation 1 we need to make at most  $2^{w^2}$  copies of each  $[p_{g_k}, Q_k]$  for  $k \in [w]$ . Hence, the size of the resulting formula will blow up by a factor of  $2w2^w2^{w^2} \leq 2^{2w^2}$  at every induction step.

Let s(l, w) and d(l, w) denote the size and depth of the new circuit  $D^{p_h,T}$ . Then from the construction above, we have the recurrences

$$s(l, w) \le 2^{2w^2} s(l', w) + 2^{w^2} \le 2^{3w^2} s(\lceil l/2 \rceil, w)$$

$$d(l, w) \le d(\lceil l/2 \rceil, w) + O(w^2)$$

Note that  $l' = \lceil l/2 \rceil$  satisfies  $l' \leq 3l/4$ . Suppose that by induction,  $s(l', w) \leq 2^{w^2}(l')^{cw^2}$  for some constant c to be chosen later. So

$$s(l,w) \leq 2^{3w^2} 2^{w^2} (l')^{cw^2} \leq 2^{4w^2} (3l/4)^{cw^2}$$

$$= 2^{w^2} l^{cw^2} \left[ 2^{3w^2} (3/4)^{cw^2} \right] \leq 2^{w^2} l^{cw^2}$$

where the last inequality holds whenever  $8(3/4)^c \leq 1$ , say  $c \geq 25$ .

Similarly, solving the recurrence for d(l, w) gives  $d(l, w) = O(w^2 \log l)$ .

**Proof:** [of lemma 6] We first relabel all the nodes at the lowest level by new variables  $z_1, \ldots, z_w$ . Then, applying Lemma 7, we obtain circuits for  $[p_g, T]$ , where g is an output gate of C' and  $T \subseteq \{1, \ldots, w\}$ . Now, to compute  $p_g$ , we sum over all T the values  $[p_g, T] \times \prod_{j \in T} val(z_j)$ , where  $val(z_j)$  denotes the original variable for which  $z_j$  was substituted. This adds O(w) to the overall depth of the circuit, thus resulting an overall depth of  $O((w + w^2 \log l)) = O(w^2 \log l)$ . The resulting circuit size is bounded by  $O(s2^w)$ , where s is an upper bound on the size of the circuits constructed in Lemma 7, and hence is bounded by  $O(2^{w^2}l^{25w^2}) \blacksquare$

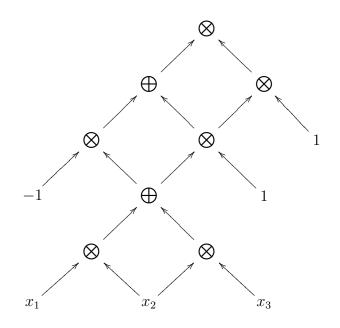

**Remark 8** If the constant-width circuit C we start with is multilinear but not syntactic multilinear, then the circuits A as in Lemma 7 need not be multilinear in the slice variables Z. This is the place where the above construction crucially uses syntactic multilinearity, and does not generalize to multilinear circuits. See Figure 5 for an example.

## 4 Making a Circuit Skew

The purpose of this section is to give a direct simulation of width bounded syntactic multilinear circuits by syntactic multilinear ABPs, yielding the following theorem.

### $\mathbf{Theorem} \ \mathbf{9} \ \mathsf{sm-VsSC}^0 \subseteq \mathsf{sm-VBWBP}$

As  $sm-VBWBP \subseteq sm-VsSC^0$  is trivially true, this, along with Theorem 3 from the previous section, gives the following relations:

#### Theorem 10 sm-VBWBP = sm-VsSC<sup>0</sup> $\subseteq$ sm-VNC<sup>1</sup>.

To establish Theorem 9, we proceed as follows. If we use the standard series-parallel construction on a circuit which is not a formula, the size of the resulting ABP can blow up exponentially in the depth of the original circuit (irrespective of its width). But in the case of a syntactic multilinear circuit, one can assume by Proposition 11 that the circuit is multiplicatively disjoint (we will define this soon). Along with this, if we have a width bound of w then for every multiplication gate, one of its sub-circuits is of width at most w - 1. We exploit this fact to give, in Theorem 16, a simulation of constant width syntactic multilinear circuits by syntactic multilinear ABPs of constant width, with only a polynomial blow up in the size. Thereom 9 thus follows from Proposition 11 and Theorem 16. As a warm-up to establishing Theorem 16, we first show in Theorem 12 such a depth-reducing simulation for weakly-skew syntactically multilinear circuits of small width.

The rest of this section is organized as follows: Section 4.1 introduces the notion of multiplicatively disjoint circuits and weakly skew circuits. In section 4.2, we give a width efficient simulation of weakly skew circuits by ABPs. Section 4.3 gives width efficient simulation of MD circuits by ABPs which preserves syntactic multilinearity.

Circuit A below is obtained by replacing gates at level 2 by Z variables.

Figure 5: A is not multilinear in the slice variable  $z_2$ .

#### 4.1 Multiplicatively Disjointness and Weakly Skewness

**Multiplicatively Disjoint Circuits:** Let C be an arithmetic circuit. C is said to be *multiplicatively disjoint* (MD for short) if every multiplication gate in C operates on disjoint sub-circuits. *i.e.* if  $f = g \times h$  is a gate in C, then the sub-circuits rooted at g and h do not share any node (except the input nodes) between them (see [MP08]). We denote the multiplicatively disjoint restriction of a class by the prefix md-. *e.g.* md-VSC<sup>*i*</sup> denotes the class of family of polynomials computed by polynomial size multiplicatively disjoint arithmetic circuits of width  $O(\log^i n)$ . It is not hard to see that syntactic degree of a multiplicatively disjoint circuit is bounded by its size, hence we have md-VsSC<sup>*i*</sup> = md-VSC<sup>*i*</sup>.

An arithmetic circuit that computes polynomials of polynomial degree can be converted into an equivalent MD-circuit without significant blow up in size ([MP08]). Thus the three restrictions of MD, small syntactic degree and small degree of the output polynomial all coincide at polynomial size and hence are equal to the class VP. However, when the width of the circuit is bounded by poly(log), all these restrictions are seemingly different, with MD circuits being the weakest among them, *i.e.*  $md-VsSC^i \subseteq VsSC^i \subseteq VsSC^i$ .

A multiplicatively disjoint circuit need not be syntactic multilinear. On the other hand, a syntactic multilinear circuit is already almost multiplicatively disjoint. At any  $\times$  gate  $f = g \times h$ , no variable can appear under both g and h, and so the sub-circuits under g and h can only share constants. As long as the constants are inputs, this does not violate multiplicative disjointness. If a shared constant appears internally, then some gate must be syntactically computing the constant. However, this is redundant in a non-uniform setting. Consider any syntactic multilinear circuit C. Replace all the gates in C that syntactically compute constants (that is, they are reachable only from leaves labeled by values from  $\mathbb{K}$ ) by the values they represent, to obtain a circuit C'. Now, it is easy to see that C' is multiplicatively disjoint and syntactic multilinear, and computes the same polynomial. Thus we can assume without loss of generality that a syntactic multilinear circuit is also multiplicatively disjoint. In particular, we have

### **Proposition 11** sm-VsSC<sup>0</sup> $\subseteq$ md-sm-VsSC<sup>0</sup>.

Also, note that if the circuit C is multilinear but not syntactic multilinear, then C' will not be multiplicatively disjoint.

Weakly Skew Circuits: An arithmetic circuit C is said to be *weakly skew* if for every multiplication gate  $f = g \times h$  in C, either the edge (g, f) or the edge (h, f) is a bridge <sup>1</sup> in the underlying graph. By definition, weakly skew arithmetic circuits are also multiplicatively disjoint. We denote this restriction on a class by the prefix weaklyskew.

In [Tod92], Toda has shown that weakly skew circuits have equivalent skew circuits, *i.e.* weaklyskew-VP = VBP. Jansen, in [Jan08] extended this result and showed that weakly skew circuits are equivalent to skew circuits in the syntactic multilinear world too, *i.e.*

<sup>&</sup>lt;sup>1</sup> A bridge in a circuit is an edge by removing which the underlying undericted graph becomes disconnected.

sm-weaklyskew-VP = sm-VBP. However, the simulation in [Jan08] is not width efficient. In the next section, we present a width efficient version of the simulation in [Jan08].

#### 4.2 Weakly Skew to Skew

In this section we give a simulation of weakly skew syntactic multilinear constant width arithmetic circuits by syntactic multilinear ABPs of constant width. This construction serves as a simpler case of the simulation given in the next section. We include it here since we achieve a slightly better size bound, which allows us to translate the result to higher width (see Corollary 15).

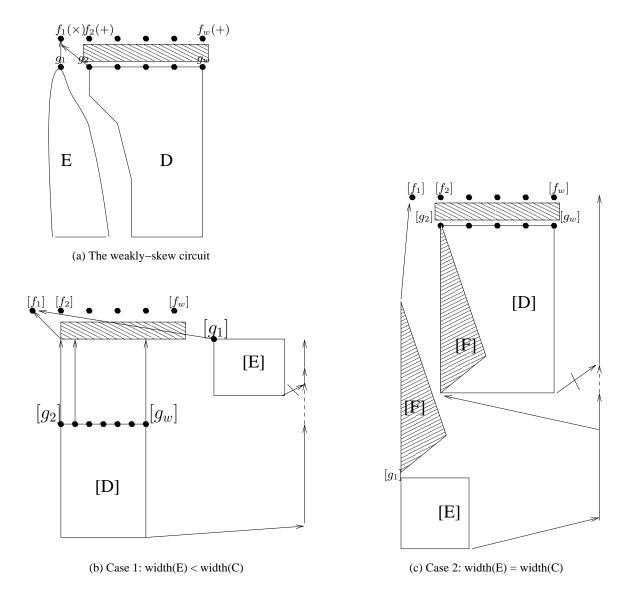

We briefly outline the overall idea: Essentially, we do the series-parallel construction. Let C be the given weakly skew circuit of width w. All the + gates in C are left untouched. For a multiplication gate  $f = g \times h$ , let  $C_h$ , the sub-circuit rooted at h, be not connected to rest of the circuit. If width $(C_h) \leq w - 1$ , then we are in good shape, since by placing the ABP [h] (available by induction on the structure of C) in series with (and after) [g] (again available by induction) we can obtain a width bound of  $O(w^2)$ . If width $(C_h) = w$ , then we have width $(C_g) \leq w - 1$ . In this case, we make a copy of [g] and place it in series with (and after) [h] and again can obtain a width bound of  $O(w^2)$ , but the size can blow up. Using a careful analysis we argue that size of the new ABP can be bounded by  $O(2^w s)$ , where s is the size of C. Now we state the main theorem:

**Theorem 12** Bounded-width weakly skew circuits can be made skew.

weaklyskew-VsSC $^0$  = VBWBP. weaklyskew-sm-VsSC $^0$  = sm-VBWBP.

**Proof:** We use the following normal form for circuits:

**Lemma 13** Let C be an arithmetic circuit of width w and size s. Then there is an equivalent arithmetic circuit C' of width O(w) and size poly(s) such that fan-in and fan-out of every gate is bounded by two, and every layer has at most one  $\times$  gate. Moreover, C' preserves any of the properties of syntactic multilinearity, weakly skewness and multiplicatively disjointness.

**Proof:** Let k be a bound on maximum fan-in and fan-out of C. First we can reduce the fan-in to two by staggering the circuit and keeping copies of the gates as and when needed. This blows up the width to 2w and size to wks. Now in a similar manner we can ensure that the fan-out of a gate is bounded by two and the size blow up will now be  $w^2k^2s$  and width will be 4w. To ensure the second condition we need to push the gates (using staggering and dummy + gates) up by at most 4w levels, thus making the total width 8w and size  $2w^2k^2s$ . Since  $k \leq w + n$  and  $w \leq s$  we have size bounded by poly(s, n).

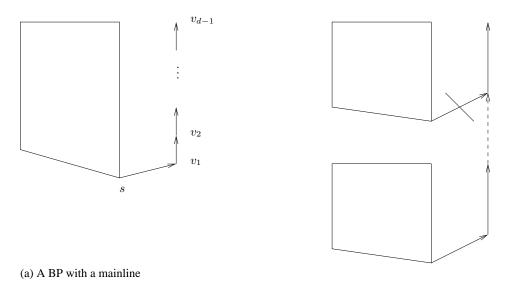

We need some more definitions and notations. For an ABP B of depth d with a single source s, we say B is endowed with a mainline, if there exist nodes  $v_1, v_2, \ldots, v_{d-1}$  reachable only along the path  $s, v_1, v_2, \ldots, v_{d-1}$ , and if the labels on this path are all set to the field

(b) Piping two mainlines

Figure 6: BPs with mainlines

constant 1. See Figure 6(a). For ABPs  $B_1$  and  $B_2$ , *piping* the mainline of  $B_1$  into the mainline of  $B_2$  is the operation of removing the edge from the source of  $B_2$  to the first node v of the mainline of  $B_2$ , and adding an edge from the last node w of the mainline of  $B_1$  to v. See Figure 6(b).

The following lemma now gives the theorem 12:

**Lemma 14** Let C be a weakly skew arithmetic circuit of width w > 1 and size s > 1 in the normal form as given by Lemma 13. Let  $f_1, \ldots, f_w$  be the output gates of C. Then there is an equivalent ABP [C] of width  $w^2 + 1$ , depth  $2^w s$  and size  $(w^2 + 1)2^w s$ . [C] has a single start node b and terminal nodes  $[f_1], \ldots, [f_w], v$  and will be endowed with a mainline ending in v. Moreover, if C is syntactically multilinear then so is [C].

**Proof:** We proceed by induction on s+w. If s = 2, the lemma holds trivially. If w = 2, then C is a skew-circuit and can be seen as an ABP of width 3 (We also need to add a mainline; hence, width is 3).

Let s > 2 and w > 2 be given, and assume that C has at least 2 layers. By the induction hypothesis, the lemma holds for all circuits of size s' and w', where either s' < s and  $w' \leq w$  or  $s' \leq s$  and w' < w.

Without loss of generality, assume that  $f_1$  is a  $\times$  gate and  $f_2, \ldots, f_w$  are + gates. Let C' be the circuit obtained by removing the output gates of C. Let  $g_1, \ldots, g_w$  be the output gates of C'. Assume that (without loss of generality)  $f_1 = g_1 \times g_2$ , and also that the edge  $(g_1, f_1)$  is a bridge in the circuit. We define the sub-circuits D and E of C' as follows: D is obtained from C' by deleting the sub-circuit rooted at  $g_1$ , E is the sub-circuit rooted at

$g_1$ . See Figure 7(a). Let s' = size(C'), w' = width(C'),  $s_J = \text{size}(J)$  and  $w_J = \text{width}(J)$  for  $J \in \{D, E\}$ . Note that s = s' + w, and  $s_J < s$  for  $J \in \{D, E\}$ .

By the induction hypothesis, we have branching programs [D] and [E], both endowed with a mainline. Let  $[g_1], v'$  denote the output of [E] and  $[g_2], \ldots, [g_w], v''$  denote the output nodes of [D], where v' and v'' are the last nodes on the mainlines. Let [F] be the subprogram of [D], which consists of all paths from the source of [D] to  $[g_2]$  and v''. Construct the program [C] with output nodes  $[f_1], \ldots, [f_w], v$  as follows: **case 1:**  $w_E \leq w - 1$ .

We compose the ABPs [D] followed by [E] as described below. (See Figure 7(b).)

- 1. For  $i, j \ge 2$ ,  $[g_j]$  has an edge to  $[f_i]$  if and only if  $g_j$  is an input to  $f_i$ .

- 2. For input gates  $f_i$ , draw an edge from v'' to  $[f_i]$  with the appropriate label.

- 3. Identify  $[g_2]$  with the start node of [E] and relabel the output node of [E] as  $[f_1]$ . Pipe the mainline of [D] into the mainline of [E].

- 4. Stagger the nodes  $[f_2], \ldots, [f_w]$  until the last level of the new program.

Size and width analysis: By the induction hypothesis, we have

width([E])

$$\leq (w_E)^2 + 1 \leq (w-1)^2 + 1$$

width([D])  $\leq w^2 + 1$

length([E])  $\leq 2^{w-1}size(E)$

length([D])  $\leq 2^w size(D)$

Hence width([C]) = max{width([D]), width([E]) + w - 1} \le w^2 + 1 and

length([C]) = length([D]) + length([E)]

$$\le 2^{w_D} s_D + 2^{w_E} s_E$$

$$\le 2^w s_D + 2^{w-1} s_E \le 2^w s \text{ (as } s = s_D + s_E + w).$$

case 2:  $w_E = w$ , and hence  $w_F \le w - 1$  and  $w_D \le w - 1$ . We compose ABPs [E], [F] and [D] as follows. (See Figure 7(c).)

- 1. Identify  $[g_1]$  with the source of [F], and pipe the mainline of [E] into the mainline of [F].

- 2. Add an edge from v' (last node of mainline of [F]) to the source of [D],

- 3. Pipe the mainline of [F] into the mainline of [D].

- 4. Alongside [D] stagger the output of [F] (which now equals  $[f_1]$ ).

Figure 7: Weakly skew circuits to skew circuits

- 5. For  $i, j \ge 2$ ,  $[g_j]$  has an edge to  $[f_i]$  if and only if  $g_j$  is an input to  $f_i$ .

- 6. Finally, for input gates  $f_i$ , draw an edge  $(v'', [f_i])$  with the appropriate label.

Size and width analysis: By induction hypothesis,

width([E])

$$\leq w^2 + 1$$

width([D])  $\leq (w - 1)^2 + 1$

width([F])  $\leq (w - 1)^2 + 1$

Observe that

$$\begin{aligned} \mathsf{width}([C]) &\leq \max(\mathsf{width}([E]),\mathsf{width}([F]),\mathsf{width}([D])+1) \\ &\leq w^2+1 \end{aligned}$$

Further, length([C]) = length([E]) + length([F]) + length([D]) + 1

$$\leq 2^{w}s_{E} + 2^{w-1}s_{F} + 2^{w-1}s_{D} + 1$$

$$\leq 2^{w}(s_{D} + s_{E}) + 1 \leq 2^{w}s.$$

Since the size of a layered ABP is length  $\times$  width, we have the required size bound. If C was syntactic multilinear to start with, then it is easy to see that so is [C].

This completes the proof of Theorem 12.  $\blacksquare$

By the parameters in the Lemma 14, it is not hard to see that if we start with a syntactic multilinear weakly skew circuit of width  $O(\log n)$ , we get a syntactic multilinear ABP of width  $O(\log^2 n)$ , *i.e.*

Corollary 15 weaklyskew-sm-VsSC<sup>1</sup>  $\subseteq$  sm-VBP[width =  $\log^2 n$ ].

#### 4.3 Multiplicatively Disjoint to Skew

We extend the simulation in Lemma 14, and hence Theorem 12, to multiplicatively disjoint circuits.

**Theorem 16** Bounded-width multiplicatively disjoint circuits can be made skew.

$$\mathsf{md}\text{-}\mathsf{VsSC}^0 = \mathsf{VBWBP}.$$

$\mathsf{md}\text{-}\mathsf{sm}\text{-}\mathsf{VsSC}^0 = \mathsf{sm}\text{-}\mathsf{VBWBP}.$

The theorem follows directly from the lemma stated below. The idea is same as that used in Lemma 14, but with a weaker bound on the size of the resulting ABP:  $O(s^w)$  instead of  $O(2^w s)$ . **Lemma 17** C be a multiplicatively disjoint arithmetic circuit of width w and size s in the normal form as given by Lemma 13. Let  $f_1, \ldots, f_w$  be the output gates of C. Then there exists an equivalent arithmetic branching program [C] of width  $O(w^2)$ , length  $O(s^w)$ , and size  $O(w^2s^w)$ . [C] has a single start node b and terminal nodes  $[f_1], \ldots, [f_w], v$ , and is endowed with a mainline ending in v. Moreover, if C is syntactic multilinear, then so is [C].

**Proof:** We proceed by induction on s + w. If s = 2, the lemma holds trivially. If w = 2, C is a weakly skew circuit, and hence can be seen as a BP of width 5.

Let s > 2 and w > 2 be given, and assume that C has at least 2 layers. Suppose, by induction hypothesis that the lemma holds for all circuits of size s' and w', where either s' < s and  $w' \leq w$  or  $s' \leq s$  and w' < w.

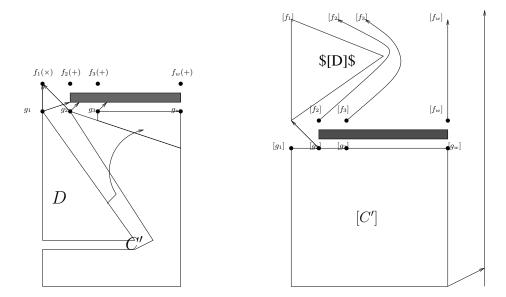

Let C' be the sub-circuit obtained by deleting  $f_1, \ldots, f_w$ . Let  $G = \{g_1, \ldots, g_w\}$  be the output gates of C'. Without loss of generality, let  $f_1 = g_1 \times g_2$  be the only multiplication gate at the output layer of C. Let D denote the sub-circuit rooted at  $g_1$  and E be the sub-circuit rooted at  $g_2$ . Since C is multiplicatively disjoint, we have either width $(D) \leq w - 1$  or width $(E) \leq w - 1$ . Without loss of generality, assume that width $(D) \leq w - 1$ .

Let s' = size(C'),  $s_D = \text{size}(D)$ , w' = width(C'), and  $w_D = \text{width}(D)$ . By induction hypothesis, we obtain ABPs [C'] and [D]. [C'] has w+1 output nodes, namely  $[g_1], \ldots, [g_w], v$ . [D] has two output nodes  $[g'_1]$  and v'.

Now construct the ABP [C] with output nodes  $[f_1], \ldots, [f_w], v$  by composing [C'] followed by [D] as follows: For all  $i \geq 2$ , connect  $[g_j]s$  to  $[f_i]s$  according to the edges in the circuit C, i.e edge  $([g_j], [f_i])$  is in [C] if and only if  $g_j$  is an input for  $f_i$ . In case  $f_i$  is an input gate, draw an appropriately labeled edge from v. Put an edge from  $[g_2]$  to  $[f_1]$ . Now identify the start node of [D] with  $[f_1]$  and re-label the terminal node of [D] as  $[f_1]$ . Do the necessary staggerings to carry on the values  $f_2, \ldots, f_w$  to the last layer. We also pipe the mainline of [C'] into the mainline of [D].

Analysis: As s' = s - w and  $w' \leq w$ , using the induction hypothesis we have

$$\mathsf{length}([C']) \le s'^{w'} \le (s-w)^w$$

Furthermore, as  $s_D \leq s - w$  and  $w_D \leq w - 1$ , we have

$$\begin{aligned} \mathsf{width}([C']) &\leq w'^2 + 1 \leq w^2 + 1 \\ \mathsf{length}([D]) &\leq s_D^{w_D} \leq (s - w)^{w - 1} \\ \mathsf{width}([D]) &\leq (w - 1)^2 + 1 \end{aligned}$$

Now, by the construction,

$$\begin{aligned} \mathsf{width}([C]) &= \max\{\mathsf{width}([C']),\mathsf{width}([D]) + w - 1\} \\ &\leq \max\{w^2 + 1, (w - 1)^2 + w - 1\} \le w^2 + 1 \end{aligned}$$

Also,

$$\begin{aligned} \mathsf{length}([C]) &= \; \mathsf{length}([C']) + \mathsf{length}([D]) \\ &\leq \; (s-w)^w + (s-w)^{w-1} \leq s^w \end{aligned}$$

Figure 8: Multiplicatively disjoint to skew

for w > 2 and w < s. Thus, size $([C]) = (w^2 + 1)s^w$ . It is easy to see that this construction preserves the syntactic multilinearity property.

Note that Lemma 17 works for all multiplicatively disjoint circuits. Consequently, the class  $md-VSC^0$  becomes the "largest" fragment of  $VsSC^0$  known to us, that is still equivalent to  $VNC^1 = VBWBP$ . Recall that  $md-VsSC^0 = md-VSC^0$ . We summarize the situation as follows:

Corollary 18 weaklyskew-VSC<sup>0</sup> = md-VSC<sup>0</sup> = VNC<sup>1</sup> = VBWBP

**Remark 19** The simulation in the case of weakly skew circuits from Lemma 14 does carry over to multilinear circuits. However as a multilinear circuit need not be multiplicatively disjoint (see Section 4.1), Lemma 17 does not work for multilinear circuits which are not syntactic multilinear.

## 5 An Overview of Syntactic Multilinear Classes

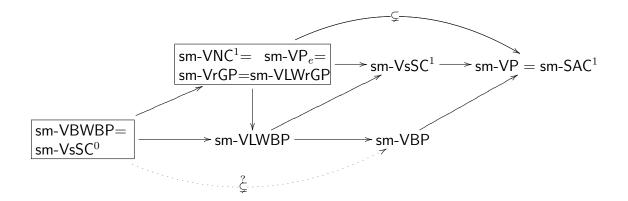

Now we turn our attention to the overall picture of the algebraic classes around  $VNC^1$  in the syntactic multilinear world. In other words, we attempt to redraw the Figure 3 when all the classes are restricted to be syntactic multilinear. We consider and compare the classes sm-VP<sub>e</sub>, sm-VNC<sup>1</sup>, sm-VsSC<sup>0</sup>, sm-VBWBP, and sm-VrGP.

A classical result from [Bre73] shows that for every arithmetic formula F of size s, there is an equivalent arithmetic formula F' which has depth  $O(\log s)$  and size poly(s). A careful observation of this proof shows that if we start with a syntactic multilinear formula F, then the depth-reduced formula F' is also syntactic multilinear. **Theorem 20** Every syntactic multilinear formula with n leaves has an equivalent syntactic multilinear circuit of depth  $O(\log n)$  and size O(n). In particular, sm-VP<sub>e</sub>  $\subseteq$  sm-VNC<sup>1</sup>.

**Proof:** By simultaneous induction on the number of leaves in the formula, we can prove the following statements. This is exactly the construction of [Bre73], analyzed carefully for syntactic multilinearity. For a formula F, let |F| denote the number of leaves in F. We inductively argue the following statements:

- (i) If F is a syntactic multilinear formula with n leaves, then there is an equivalent syntactic multilinear circuit F' of depth  $\lceil 4 \log n \rceil$  and size 2n.

- (ii) If x is any leaf in F, then we can express F as F' = Ax + B, where A, B are syntactic multilinear circuits that do not depend on x and are of depth  $\lceil 4 \log |A| \rceil$  and  $\lceil 4 \log |B| \rceil$  respectively.

In the base case, there is either a single variable or a constant, and the claim holds trivially.

Let X be a tree separator<sup>2</sup> for F, with children L, R, so that X = L op R. Replace the whole subtree under X by a new variable x. By inductive statement (ii), we have F' = Ax + B where A, B are as above (*i.e.* they are both syntactic multilinear and do not depend on X). Also by inductive statement (i), we have syntactic multilinear formulas L', R' equivalent to L, R of small depth. Thus we have  $F' = A \times (L' \text{ op } R') + B$ . Since A does not depend on any variable below X, F' is syntactic multilinear. Now, depth(F') = $\max\{\text{depth}(A) + 2, \text{depth}(L') + 3, \text{depth}(R') + 3, \text{depth}(B) + 1\} \leq \lceil 4 \log n \rceil$ .

To prove the second half of the statement above, let x be any leaf in F. Now find a tree separator X = L op R such that the subtree at one of its children, say L, contains x as a leaf and is of size < n/2. Then, by inductive statement (ii) applied to L, L' = Ax + B, where A, B are independent of x, syntactic multilinear and of small depth. Now replace the subtree at X by a new variable y. Applying inductive statement (ii), we have F' = Cy + D, where C, D are syntactic multilinear small depth formulas which do not depend on y (*i.e.* L op R). Applying inductive statement (i) to R, we have an equivalent small-depth R'.

- **Case 1:** op = +. Then F' = C((Ax + B) + R') + D = CAx + (CB + CR' + D). This is again syntactic multilinear since C does not depend on y, *i.e.* Ax + B + R.

- **Case 2:** op =  $\times$ . Then F' = C(Ax + B)R' + D = CAR'x + (CBR' + D). Here again F' is syntactic multilinear since C does not depend on A, B, R', and also because A and B do not share any variables with R'.

Since we are constructing a circuit and not a formula, we don't need to replicate the circuits for C and R'. For details about the size/depth, see the analysis in [Bre73].

It is easy to see that the path-preserving simulation of a constant width branching program by a log depth circuit preserves syntactic multilinearity:

<sup>&</sup>lt;sup>2</sup> A tree separator of F is a gate X in F so that the sub-formulas  $F_X$  and  $F \setminus F_X$  are of size at most 3/4|F|, where  $F_X$  is the sub-formula rooted at X and |F| is the number of leaves in F.

**Lemma 21** For any syntactic multilinear branching program P of width w and size s over ring  $\mathbb{K}$ , there is an equivalent syntactic multilinear circuit C of depth  $O(\log s)$  and size O(s) with fan-in of + gate bounded by w (or alternatively, depth  $O(\log w \log s)$  and bounded fanin).

In particular, sm-VBWBP  $\subseteq$  sm-VNC<sup>1</sup> and sm-VBP  $\subseteq$  sm-VSAC<sup>1</sup>.

**Proof:** Let l be the length of P(s = lw), and let  $p_{s,t}$  denote the weighted sum of the directed paths between nodes s and t. Let  $v_1, \ldots v_w$  denote the nodes at the level  $l' = \lceil l/2 \rceil$  of P. Then  $p_{s,t} = \sum_{i=1}^{w} p_{s,v_i} \times p_{v_i,t}$ . Thus the depth and size of the inductively constructed circuit satisfy the recurrences d(l) = 2 + d(l') and s(l) = (3w)s(l'), giving the desired bounds. It is clear that the circuit so constructed is syntactic multilinear; if it were not, the offending  $\times$  gate would pinpoint a path in P that reads some variable twice.

It is also straightforward to see that the construction of [IZ94], staggering a small-depth formula into a small-width one, preserves syntactic multilinearity. Thus

**Lemma 22** Let  $\Phi$  be any sm-formula with depth d and size s. Then there is an equivalent syntactic multilinear formula  $\Phi'$  of length 2s and width d. In particular, sm-VNC<sup>1</sup>  $\subseteq$  sm-VLWF.

**Proof:** For completeness we give a detailed proof here. The construction is by induction on the structure of the formula  $\Phi$ . The base case is when  $\Phi$  is a single variable or a constant, in which case the lemma holds trivially.

Suppose the lemma holds for any formula of depth at most d - 1. Consider the root gate f of a formula  $\Phi$  of depth d. Suppose  $f = \sum_{i=1}^{k} g_i$  (respectively  $f = \prod_{i=1}^{k} g_i$ ). As the depth of each formula  $g_i$  is bounded by d - 1, by induction we have formulas  $g'_i$  of width d - 1 and length bounded by  $s_i$  (the size of  $g_i$ ), computing the same function as  $g_i$ s. Place the node corresponding to f with two children. At one child, place the formula  $g'_1$ ; at the other, place a series of no-op ( *i.e.*  $\times 1$  or +0 ) gates till the last level of  $g'_1$ . Then give the last no-op gate two children, place  $g'_2$  at one child, and so on. The width of the new formula  $\Phi'$  thus obtained is bounded by  $\max_i \operatorname{width}(g'_i) + 1$ , and its length is bounded by  $\sum_i \operatorname{length}(g'_i) + 1 \leq \sum_i s_i + 1 \leq s$ . Note that in this process, for any gate g in  $\Phi$  the variables it operates on are not changed in the new formula  $\Phi'$ , that is, the only new gates which are introduced in  $\Phi'$  are the no-op gates which are used for staggering, which only multiply by the constant 1. Thus if  $\Phi$  is syntactic multilinear then so is  $\Phi$ .

From Lemma 22 and Theorem 20, we have the following equivalence.

Corollary 23 Over any ring  $\mathbb{K}$ , sm-VP<sub>e</sub> = sm-VLWF= sm-VNC<sup>1</sup> = sm-Formula-Depth,Size(log, poly).

In [AAB<sup>+</sup>99] a characterisation for bounded depth arithmetic circuits in terms of counting number of paths in a restricted version of bounded width grid graphs is presented. We note that the characterisation given in [AAB<sup>+</sup>99] works for bounded depth arithmetic circuits over arbitrary rings, showing that  $VBWrGP = VAC^{0}$ . By closely examining the parameters in [AAB<sup>+</sup>99], we obtain a characterisation for  $\mathsf{VNC}^1$  in terms of the restricted version of log width grid branching programs. We also note that these constructions preserve syntactic multilinearity. In the statement and proof below, we use the notion of alternation-depth: a circuit C of unbounded fan-in has alternation depth a if on every leaf-to-root path, the number of maximal segments of gates of the same type is at most a. Also, for an rGP (and in fact any branching program) P, we denote by  $\mathsf{Var}(P)$  the set of variables that appear on some s-to-t path in P. For a formula F,  $\mathsf{Var}(F)$  denotes the variables appearing anywhere in the formula F; if h is the root of F, then without loss of generality  $\mathsf{Var}(F) = X_h$ .

**Lemma 24** Let  $\Phi$  be an unbounded fan-in arithmetic formula of size s (i.e. number of wires) and alternation-depth 2d over  $\mathbb{K}$  and with input variables  $X \in \mathbb{K}^n$ . Then there is a restricted grid program P of length  $s^2 + 2s$  (i.e. the number of edge layers) and width  $\max\{2, 2d\}$ , where the edges are labelled from  $\operatorname{Var}(\Phi) \cup \mathbb{K}$ , such that the weighted sum of s-to-t paths in P is equal to the function computed by  $\Phi$ . Further, if  $\Phi$  is syntactic multilinear, then so is P.

**Proof:** The construction here is exactly the same as in  $[AAB^+99]$ ; it is included here for completeness in arguing, over more general parameters, that syntactic multilinearity is preserved. Without loss of generality, assume that the formula  $\Phi$  is such that all nodes in a particular layer represent the same type of gate and two successive layers have different kind of gates. Also, assume that  $\Phi$  is height balanced, *i.e.* any root to leaf path in  $\Phi$  is of length exactly 2*d*. Further assume that the root is a × gate. If these conditions do not hold, then ensuring them will blow up the size of  $\Phi$  to at most  $s^2$ , and increase the depth by at most 2. We assume that *s* and *a* are the size and alternation depth of a formula already in this normal form.

We proceed by induction on the depth of the formula  $\Phi$ . The base case is when  $d \leq 1$ . If the depth is 0, then  $\Phi$  is either a variable or a constant in the underlying ring. In this case the graph is  $G_{0,1}(c)$  where  $\Phi = c$ . If d = 1, then  $\Phi$  is a product of linear factors, and a suitable composition of  $G_{0,1}(c)$  graphs and  $G_{0,2}$  represents it.

Suppose that for any (syntactic multilinear) formula F with alternation depth 2d' < 2dand size s' (in the normal form described above), there is a (syntactic multilinear) restricted grid program P of width 2d' and length  $s'^2 + 2s'$ , where P uses variables from Var(F).

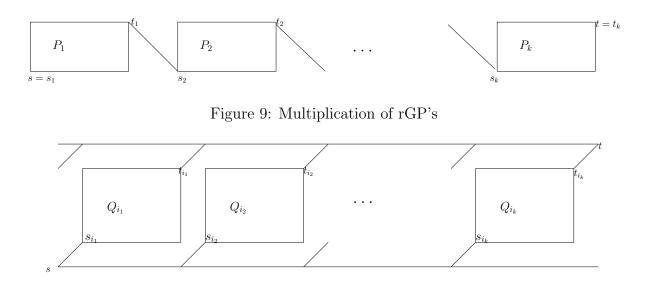

Now let  $\Phi$  be a normal form formula with alternation depth 2d. Consider the root gate g of  $\Phi$ . Let  $g_1, \ldots, g_k$  be the children of g, where  $g_i = \sum_{j=1}^{t_i} g_{i_j}$ . Let  $s_{i_j}$  and  $2d_{i_j} = 2d - 2$  respectively denote the size and alternation depth of the sub-formula rooted at  $g_{i_j}$ . Note that  $s = k + \sum_i (t_i + \sum_j s_{i_j})$ . Applying induction on the sub-formula rooted at each  $g_{i_j}$ , let  $Q_{i_j}$  denote the resulting restricted grid program for the formula at  $g_{i_j}$ . Now place the  $Q'_{i_j}$ s  $(1 \leq j \leq t_i)$  as in Figure 10 to get the program  $P_i$ , and connect the  $P_i$ 's as shown in Figure 9 to get the desired program P. By the inductive hypothesis,  $\text{length}(Q_{i_j}) \leq s_{i_j}^2 + 2s_{i_j}$  and  $\text{width}(Q_{i_j}) \leq 2d_{i_j}$ . From the construction as above, we have  $\text{length}(P_i) = t_i + 1 + \sum_j (ength(Q_{i_j}) \leq t_i + 1 + \sum_j (s_{i_j}^2 + 2s_{i_j}))$  and hence  $\text{length}(P) = k - 1 + \sum_i \text{length}(P_i) \leq k - 1 + \sum_i ((t_i + 1) + \sum_j (s_{i_j}^2 + 2s_{i_j})) \leq s^2 + 2s$ . Note that the construction in Figure 10

Figure 10: Addition of rGP's

adds 2 to the width and the construction in Figure 9 does not change the width. Hence the width of P is bounded by  $2 \max_{i,j} d_{i_j} + 2 = 2d$ .

If  $\Phi$  is syntactic multilinear, then the formulas rooted at  $g_{i_j}$  are all syntactic multilinear, and for  $i \neq i'$ ,  $\operatorname{Var}(g_i) \cap \operatorname{Var}(g_{i'}) = \emptyset$ . Thus, by the inductive hypothesis, the programs  $Q_{i_j}$  are syntactic multilinear, and only use variables from  $\operatorname{Var}(g_{i_j})$ , and hence the programs  $P_i$  (for each i) only use variables from  $\operatorname{Var}(g_i)$ . Thus for every  $i \neq i'$ ,  $\operatorname{Var}(P_i) \cap \operatorname{Var}(P_{i'}) = \emptyset$ . Since each path in the final program goes through exactly one  $Q_{i_j}$  for each i, it follows that P is syntactic read-once.

We now establish the converse to Lemma 24. The proof of the converse as in [AAB<sup>+</sup>99] is uniform and it produces a circuit rather than a formula. If we do not insist on uniformity of the circuit, then we actually get a formula. Thus it can be shown that functions computed by width 2w + 2, length l restricted grid programs can be computed (non uniformly) by formulas of depth 2w + 2 and size O(l).

**Lemma 25** Let P be an arithmetic rGP of length l (number of edge layers) and of width 2w + 2 with variables from  $X \in \mathbb{K}$ . Then there exists an equivalent arithmetic formula  $\Phi$  over  $\mathbb{K}$ , with alternation depth at most 2w + 2, size (number of wires) at most 2l, and  $Var(\Phi) = Var(P)$ .

Further, if P is syntactic multilinear, then so is  $\Phi$ .

**Proof:** Again, this construction is the same as in [AAB<sup>+</sup>99]; it is presented here with the induction unfolded to allow arguing, over more general parameters, that syntactic multilinearity is preserved.

For a program B, let f(B) denote the function computed by B. We proceed by induction on w. The base case is when w = 0, *i.e.* we have a rGP P of width 2. Then f(P) can be computed by a depth 2 formula with one  $\times$  gate as root and a number of + gates as its inputs, where the + gates get input from  $X \cup \mathbb{K}$ . The total fan-in of the + gates is bounded by the number of layers which contain the graph  $G_{0,1}(c)$ , for some c. The fan-in of the  $\times$  gate is one more than the number of layers which have the graph  $G_{0,2}$ . (The layers having  $G_{0,0}$ do not contribute to the formula.) Thus the total number of wires is bounded by  $l+1 \leq 2l$ , and depth is 2. If P is syntactic multilinear, no path reads the same variable twice, and so the inner blocks separated by  $G_{0,2}$  have disjoint sets of variables. Hence the top  $\times$  gate operates on disjoint sets of variables.

Suppose that for any w' < w the claim holds, *i.e.* for a (syntactic multilinear) rGP P' of width 2w' + 2 and length l', there is an equivalent (syntactic multilinear) formula  $\Phi'$  of depth 2w' + 2 and size 2l' and using only variables from Var(P').

Now P is the given rGP of width 2w + 2, length l. Let P be composed as  $g_1, \ldots, g_l$ . Let  $i_1 < i_2 < \ldots < i_m$  be the (uniquely defined) set of all indices where  $g_{i_1}, \ldots, g_{i_m}$  are the graph  $G_{w,2w+2}$ . Define  $i_0 = 0$ ,  $i_{m+1} = l + 1$ .

For each  $0 \leq j \leq m$ , let  $P_j$  denote the program  $g_{i_j+1}, \ldots, g_{i_{j+1}-1}$  sandwiched between the *j*th and (j+1)th incidence of  $G_{w,2w+2}$ .

The nodes  $s_j$  and  $t_j$  for each  $P_j$  are defined accordingly. Let  $l_j$  denote the length of  $P_j$ ; then  $l = m + \sum l_j$ . Note that these  $P_j$ s do not have  $G_{w,2w+2}$  at any layer, and  $f(P) = \prod_j f(P_j)$ .

Consider  $P_j$  for some j. Let  $h_{j_1}, \ldots h_{j_{r_j}}$  denote the layers of  $P_j$  which are the connecting graph  $G_{w,2w+1}$ . Let  $Q_{j,k}$  denote the part of the program between  $h_{j_k}$  and  $h_{j_{k+1}}$ , and  $Q_{j,0}$ denote the part between  $g_{i_j}$  and  $h_{j_1}$  and  $Q_{j,r_j}$  denote the part between  $h_{j_r}$  and  $g_{i_{j+1}}$ . Let  $Q'_{j,k}$ denote the graph obtained from  $Q_{j,k}$  be removing the top-most and bottom-most lines and the edges connecting them. Then width $(Q'_{j,k}) = \text{width}(Q_{j,k}) - 2 = 2w$ . Let  $l_{j,k}$  denote the length of  $Q'_{j,k}$ ; so  $l_j \leq r_j + \sum_{k=1}^{r_j-1} l_{l,k}$ . The nodes  $s'_{j,k}$  and  $t'_{j,k}$  for  $Q'_{j,k}$  are defined accordingly. Now  $f(P_j) = \sum_{k=1}^{r_j-1} f(Q'_{j,k})$ . (Note that  $Q_{j,0}$  and  $Q_{j,r_j}$ , even if non-trivial, play no role in  $f(P_j)$  because there is no connection from  $s_j$  to these blocks.)

By induction, for each  $Q'_{j,k}$  we obtain an equivalent (syntactic multilinear) formula  $\Phi_{j,k}$ with variables from  $\operatorname{Var}(Q'_{j,k})$ ,  $\operatorname{size}(\Phi_{j,k}) = s_{j,k} = 2l_{j,k}$  and  $\operatorname{depth}(\Phi_{j,k}) = d_{j,k} = 2w$ . Now define  $\Phi = \prod_j \sum_{k=1}^{r_j-1} \Phi_{j,k}$ . Then  $\operatorname{size}(\Phi) = s = m + \sum_j (r_j - 1 + \sum_k 2l_{j,k}) \leq 2l$  and  $\operatorname{depth}(\Phi) = 2w + 2$  as desired. Clearly  $\operatorname{Var}(\Phi) = \operatorname{Var}(P)$ .

If P is syntactic multilinear, then inductively we have  $\Phi_j = \sum_{k=1}^{r_j} \Phi_{j,k}$  operating on  $\operatorname{Var}(P_j)$ , and each  $\Phi_{j,k}$  is syntactic multilinear. Consider the root gate of  $\Phi$ . If it is not syntactic multilinear, then for some j < j', and for some  $k, k', \Phi_{j,k}$  and  $\Phi_{j',k'}$  use the same variable x. Thus, by induction,  $P_j$  has an  $s_j$ -to- $t_j$  path using x, and  $P_{j'}$  also has an  $s_{j'}$ -to- $t_{j'}$  path using x. Combining these paths with (1) the s-to- $s_j$  path along the bottom-line, (2) the  $t_j$ -to- $s_{j'}$  path using  $g_{i_j+1}$  and then the bottom line, and (3) the  $t_{j'}$ -to-t path along the top line, gives a path in P that reads x twice, contradicting the read-once property of P.

As an immediate consequence of the above two lemmas, we have:

Corollary 26 1. sm-VAC<sup>0</sup> = sm-VBWrGP;

Figure 11: Relationship among syntactic multilinear classes

2.  $VNC^1 = VrGP = VLWrGP$ .

3.  $sm-VNC^1 = sm-VrGP = sm-VLWrGP;$

**Proof:** (1) follows from Lemmas 24 and 25. For (2), note that  $VrGP \subseteq VP_e$  from Lemma 25 and  $VP_e \subseteq VrGP$  using Lemma 25. As  $VP_e = VNC^1$ , (2) follows. As  $sm-VP_e = sm-VNC^1$  by Theorem 20, we have the equivalence in (3).

Further, noting that the constructions do not introduce constants other than 0 and 1, we see that they hold in the Boolean setting as well. Thus.

Corollary 27  $NC^1 = rGP = LWrGP$ .

We summarize these relationships in Figure 11.

## 6 Coefficient Functions

Let f be a polynomial over variables  $X = \{x_1, x_2, \ldots, x_n\}$ ; we denote this by Var(f) = X. For a monomial m in variables from X, the partial coefficient function coef(f, m) is defined to be the unique polynomial g such that f can be written as f = mg + h, where h is a polynomial with none of its monomials divisible by m.

Malod studies the complexity of computing coefficient functions computed by class of arithmetic circuits [Mal07]. From an old observation by Hammon, it can be seen that the permanent polynomial equals  $\operatorname{coef}(f, y_1y_2 \dots y_n)$ , where f is given by the depth-3 formula  $f = \prod_{i \in [n]} \sum_{j \in [n]} x_{ij}y_j$ . In [Mal07] it is shown that the Hamiltonian polynomial can be represented as a coefficient of a polynomial g computed by polynomial size arithmetic circuits. A closer inspection shows that this polynomial g is actually in VBP. Thus arithmetic circuit classes which are only as powerful as VAC<sup>0</sup> or VBP can generate VNP-complete polynomials as coefficient functions, and hence the coefficient functions are hard in general.

In the case of polynomials computed by syntactic multilinear circuits we will prove that the situation is markedly different compared to the general case. For a multilinear polynomial f over variables  $x_1, x_2, \ldots, x_n$ , we define the coefficient function  $mcoef(f, \cdot)$  as follows:

for each  $a = a_1 a_2 \dots a_n \in \{0, 1\}^n$ ,  $\mathsf{mcoef}(f, a) = \mathsf{coef}(f, x_1^{a_1} x_2^{a_2} \dots x_n^{a_n})$ .

Corresponding to  $mcoef(f, \cdot)$ , there is a unique multilinear polynomial g(x, e) in variables from X and E, such that for all  $a \in \{0, 1\}^n$ , g(x, a) = mcoef(f, a) defined by

$$g(x,e) = \sum_{b \in \{0,1\}^n} \mathsf{mcoef}(f,b) \prod_{i=1}^n \left( e_i b_i + (1-e_i)(1-b_i) \right)$$

. With some abuse of notation we will denote this polynomial g by mcoef(f, e).

#### 6.1 Closure Property

A syntactically multilinear complexity class sm-C is said to be *closed under taking coefficients*, if for any polynomial  $f \in \text{sm-}C$ , the polynomial mcoef(f, e) is also in sm-C. We have the following identities:

For any polynomials f and g,

$$mcoef(f + g, e) = mcoef(f, e) + mcoef(g, e)$$

(2)

As the partial coefficient of  $x_1^{a_1} \cdots x_n^{a_n}$  in f + g is the sum of the coefficient of  $x_1^{a_1} \cdots x_n^{a_n}$  in f and g, for all  $a_1, \ldots, a_n \in \{0, 1\}$ .

Let f and g be multilinear polynomials in  $\mathbb{K}[x_1, \ldots, x_n]$  with  $\mathsf{Var}(f) \cap \mathsf{Var}(g) = \emptyset$ . For  $a_1, \ldots, a_n \in \{0, 1\}$ , if there is an i such that  $a_i = 1$  and  $x_i \notin \mathsf{Var} f \cup \mathsf{Var}(g)$  then the partial coefficient of  $x_1^{a_1} \cdots x_n^{a_n}$  is zero. As  $\mathsf{Var}(f) \cap \mathsf{Var}(g) = \emptyset$ , the monomial  $x_1^{a_1} \cdots x_n^{a_n}$  factors across f and g in a unique way, *i.e.*

$$\mathsf{mcoef}(fg, e) = \mathsf{mcoef}(f, e^f) \cdot \mathsf{mcoef}(g, e^g) \cdot \left(\prod_{x_i \notin \mathsf{Var}(f) \cup \mathsf{Var}(g)} (1 - e_i)\right)$$

(3)

where  $e^f$  and  $e^g$  are the projection of e to Var(f) and Var(g) (*i.e.*  $e^f_i = 0$  for  $x_i \notin Var(f)$ ,  $e^f_i = e_i$  for  $x_i \in Var(f)$ ; similarly for  $e^g$ ).

For individual variables  $x_i$  and constants  $\mu$  we have

$$\mathsf{mcoef}(x_i, e) = (x_i(1 - e_i) + e_i) \left(\prod_{j \in [n], j \neq i} (1 - e_j)\right)$$

(4)

$$\mathsf{mcoef}(\mu, e) = \mu\left(\prod_{j \in [n]} (1 - e_j)\right) \tag{5}$$

**Theorem 28** Each of the following syntactically multilinear classes is closed under taking coefficients: sm-VP, sm-VBP, sm-VNC<sup>1</sup>, sm-VSC<sup>i</sup>, sm-VBWBP, and sm-VAC<sup>i</sup>, for all  $i \ge 0$ .

#### **Proof:**

Let C be a syntactic multilinear circuit computing the polynomial f. Construct a circuit C' on variables  $X = \{x_1, \ldots, x_n\} \cup e = \{e_1 \ldots, e_n\} =$  inductively as follows:

Base Case

$$-C = a \in \mathbb{K}$$

, then  $C' = a(\mu(\prod_{j \in [n]} (1 - e_j)))$

$-C = x_i \text{ for } 1 \le i \le n$ , then  $C' = (x_i(1 - e_i) + e_i)(\prod_{j \in [n], j \ne i} (1 - e_j)).$

Induction  $-C = C_1 + C_2$  and suppose  $C'_1$  and  $C'_2$  are circuits obtained from induction. Then  $C'(X, e) = C'_1(X, e) + C'_2(X, e).$

$$-C = C_1 \times C_2, \text{ let } C'_1 \text{ and } C'_2 \text{ be availabe by induction. Then } C'(X, e) = C'_1(X, e') \times C'_2(X, e'') \times \left(\prod_{x_i \notin \mathsf{Var}(C_1) \cup \mathsf{Var}(C_2)}(1 - e_i)\right). \text{ Where } e' = \{e_i \mid x_i \in \mathsf{Var}(C_1)\} \text{ and } e'' = \{e_j \mid x_j \in \mathsf{Var}(C_2)\}.$$

We first argue that C' is syntactic multilinear. The construction for the base case is trivially syntactic multilinear. When  $C = C_1 + C_2$ , by induction hypothesis  $C'_1$  and  $C'_2$  are syntactic multilinear, so  $C' = C'_1 + C'_2$  is also syntactic multilinear. For  $C = C_1 \times C_2$ , as  $Var(C_1) \cap$  $Var(C_2) = emptyset$ , we have  $e' \cap e'' = \emptyset$ . So, by definition  $Var(C'_1(X, e') \cap Var(C'_2(X, e'')) = \emptyset$ . As the  $e_i$ s that appear in the product  $\prod_{x_i \notin Var(C_1) \cup Var(C_2)} (1 - e_i)$  do not appear in either  $C'_1(X, e')$  or  $C'_2(X, e'')$ , we have C' is syntactic multilinear.