# **Basic Illustrations**

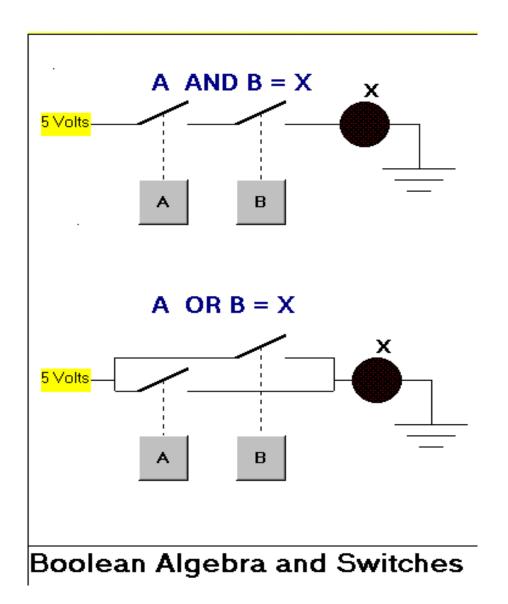

Functions/units of CPU;

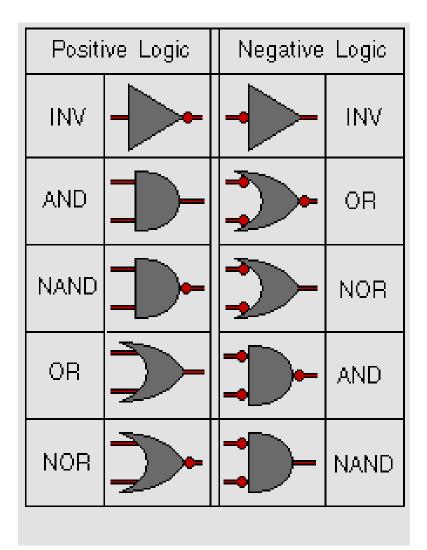

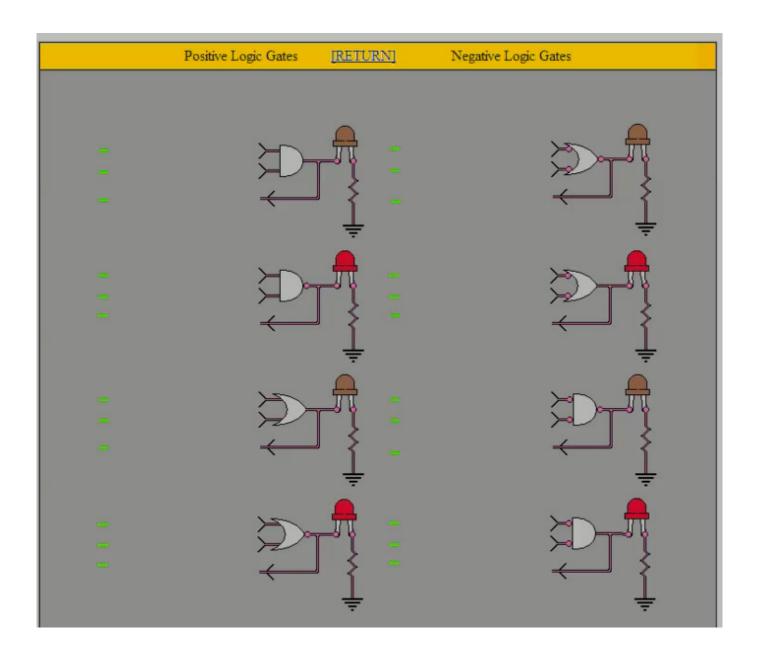

Followed by logic gates.

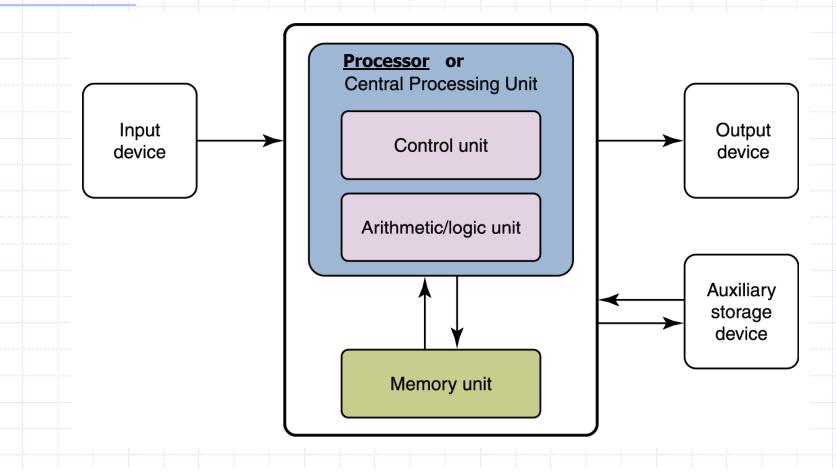

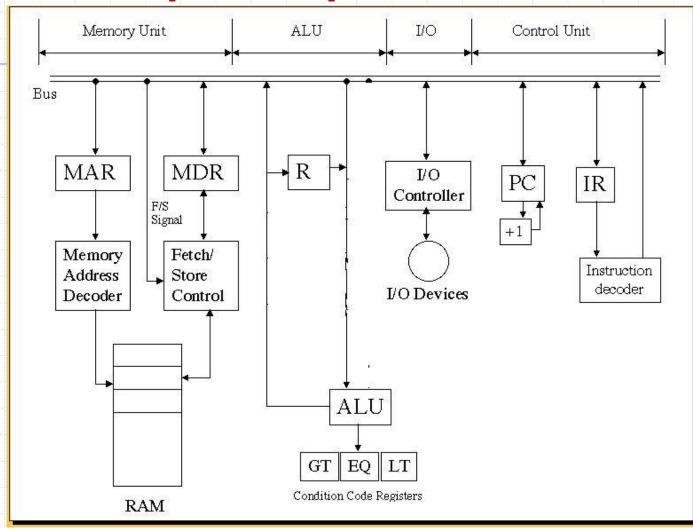

# The von Neumann Architecture of a Computer

3

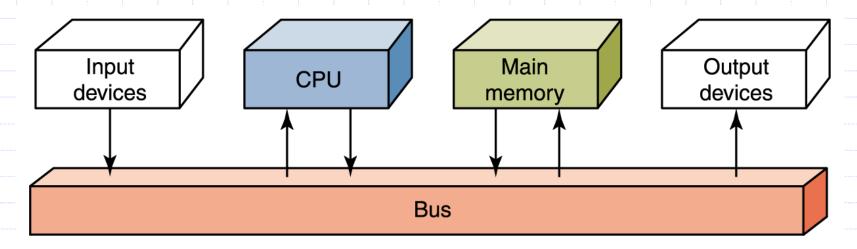

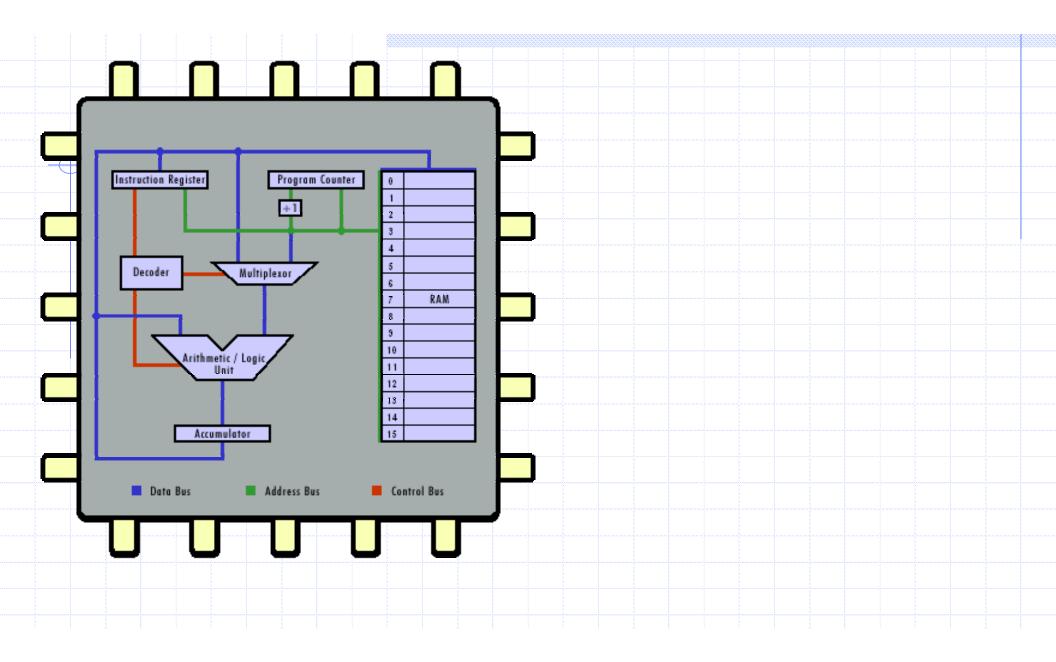

## Simple single-bus architecture

The parts are inter-connected by a collection of wires called a "bus".

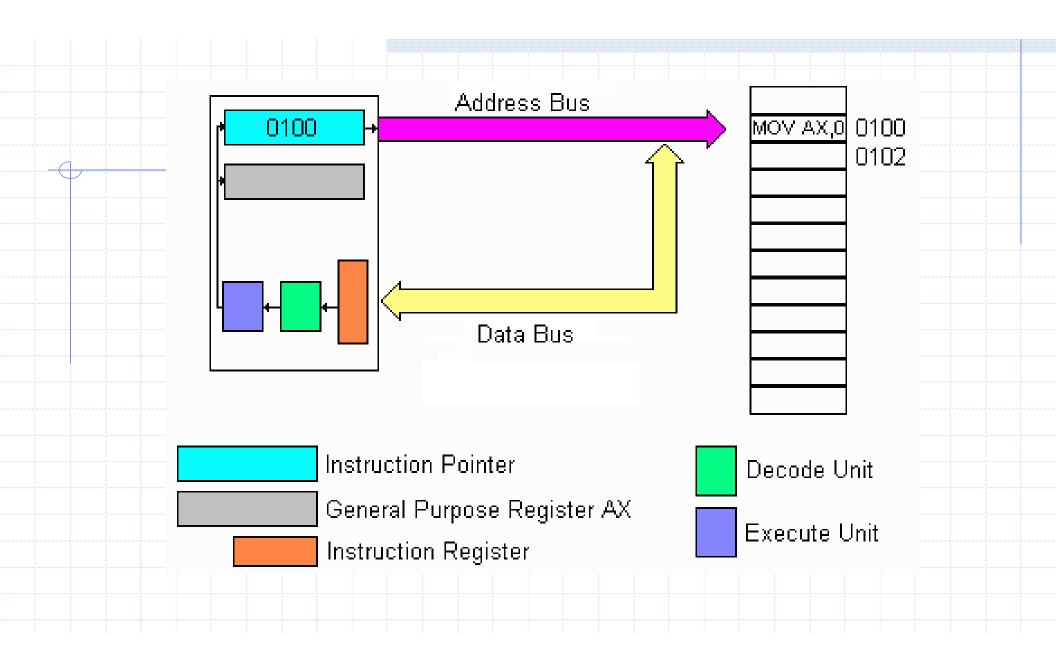

Data flow through a von Neumann architecture

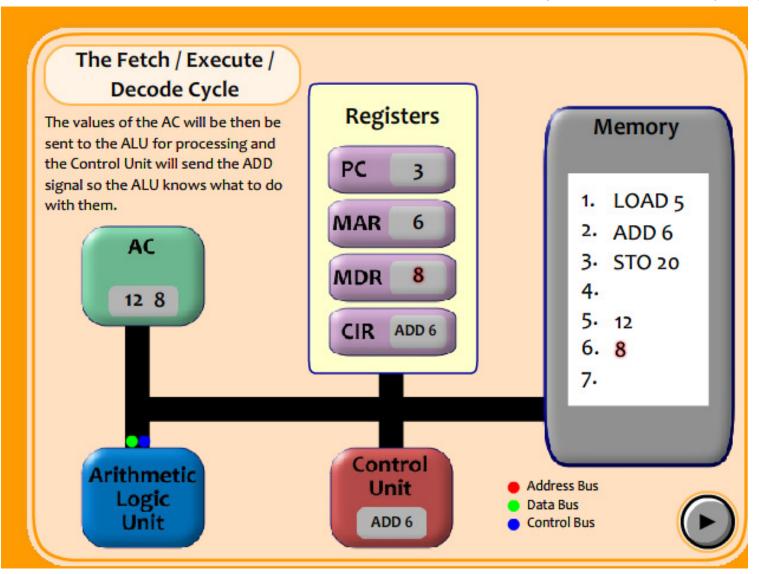

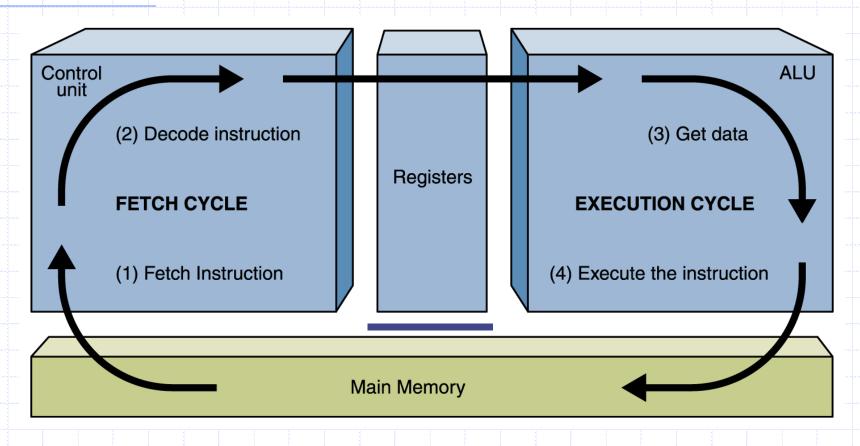

### **The Fetch-Execute Cycle**

## **A simple Computer Architecture**

8

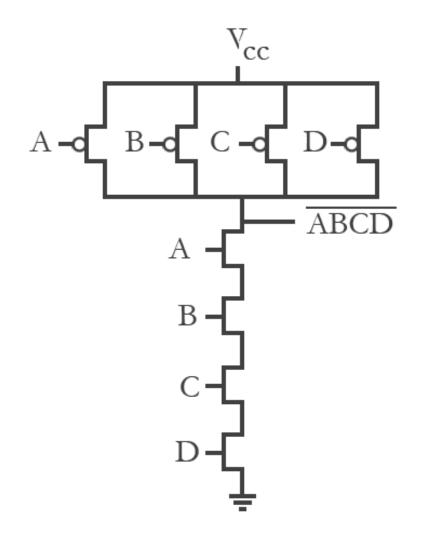

#### **Categories in Digital System Design:**

- System Level

- Logical level

- Circuit Level

#### **Types of Switching Network:**

- Combinatorial

- Sequential

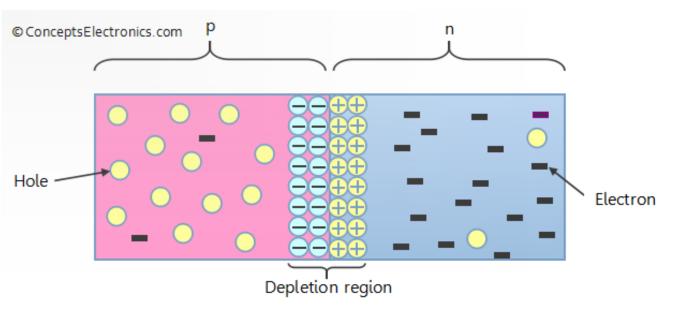

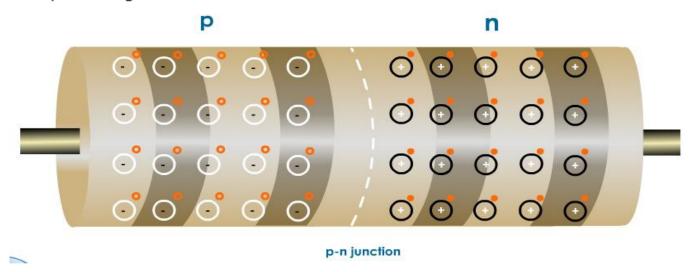

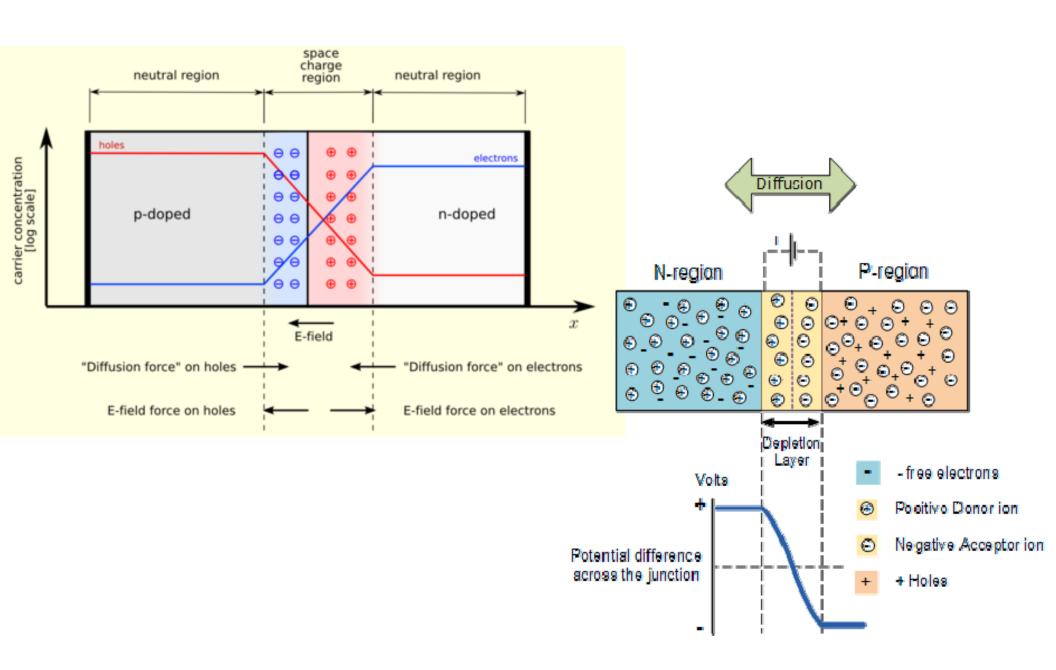

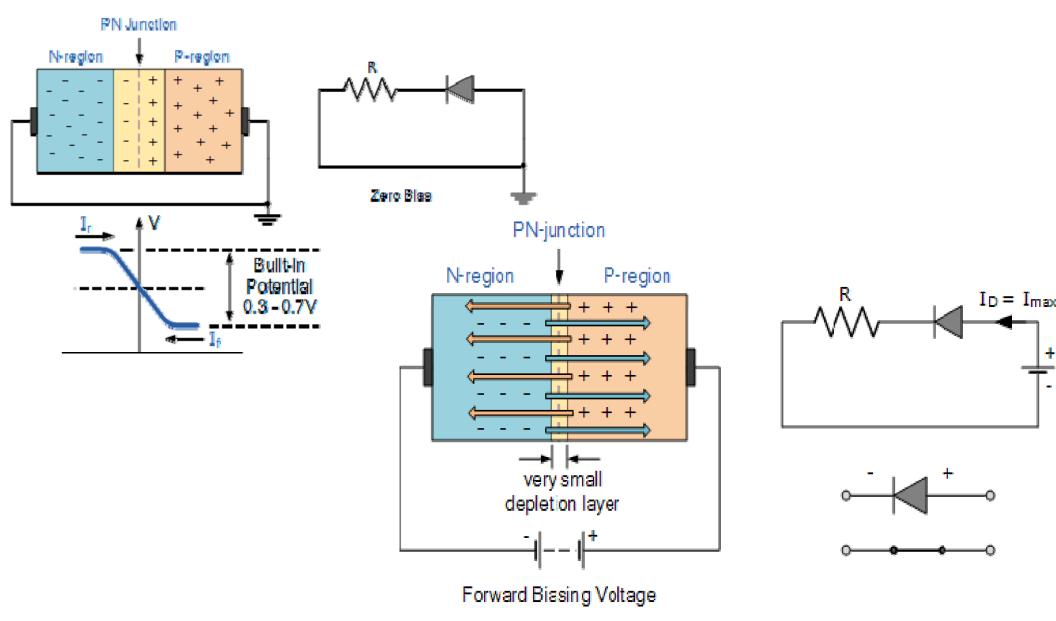

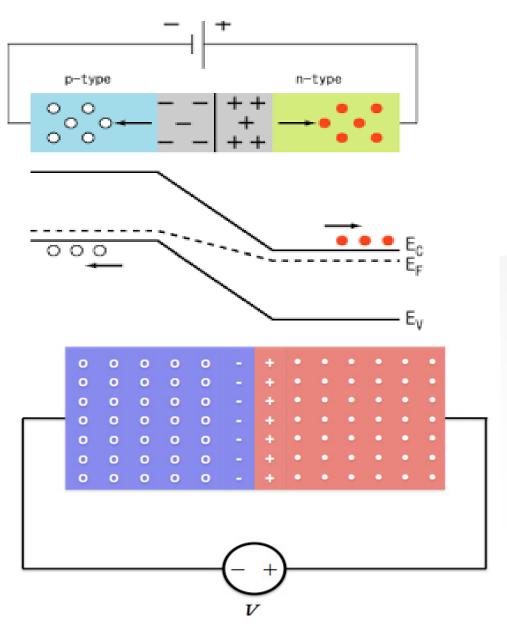

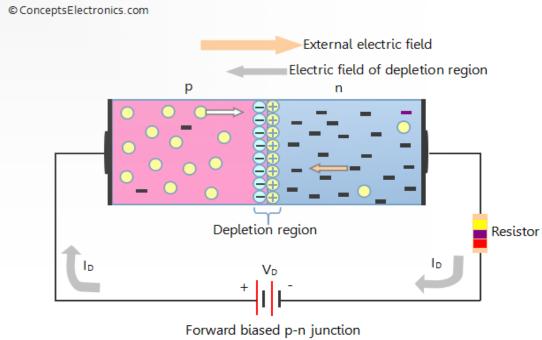

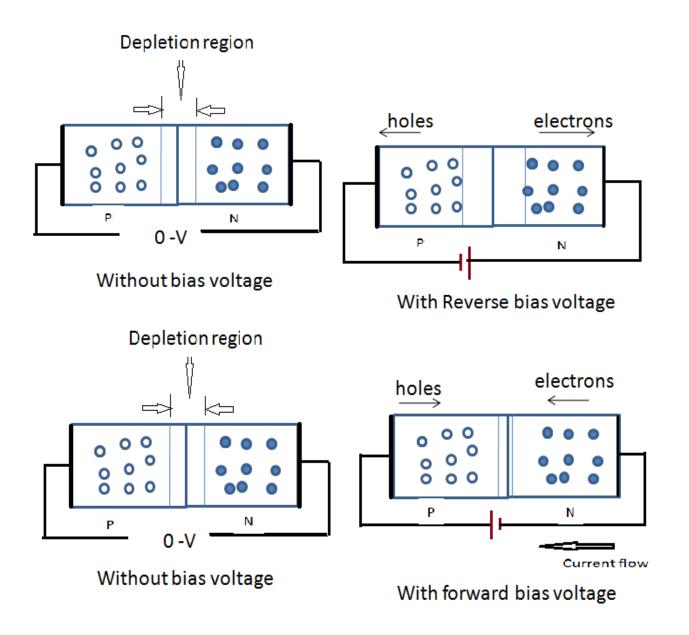

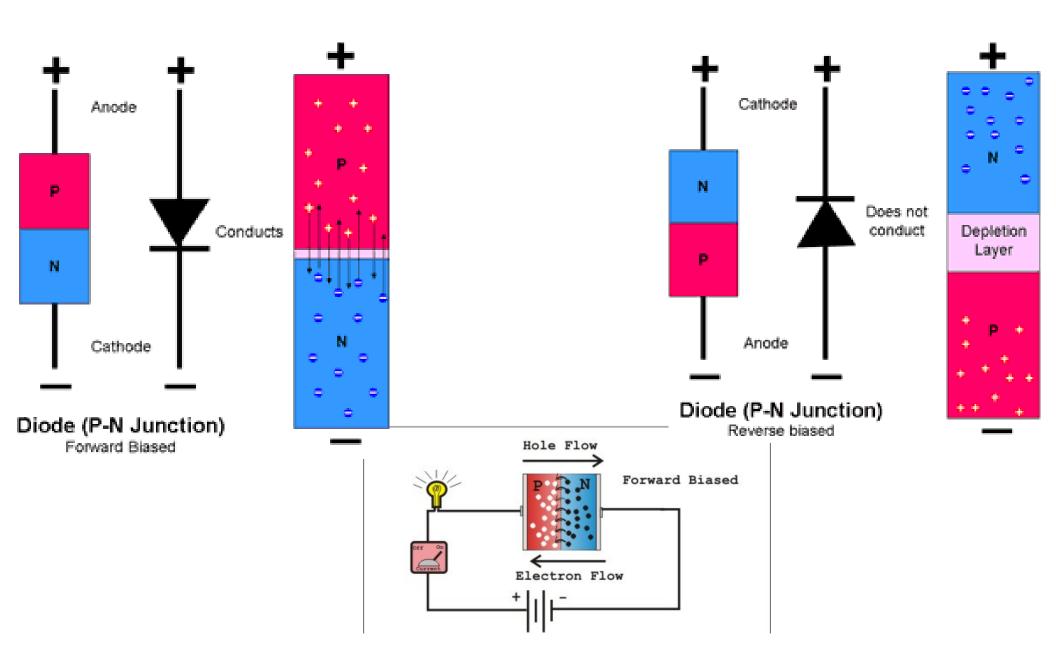

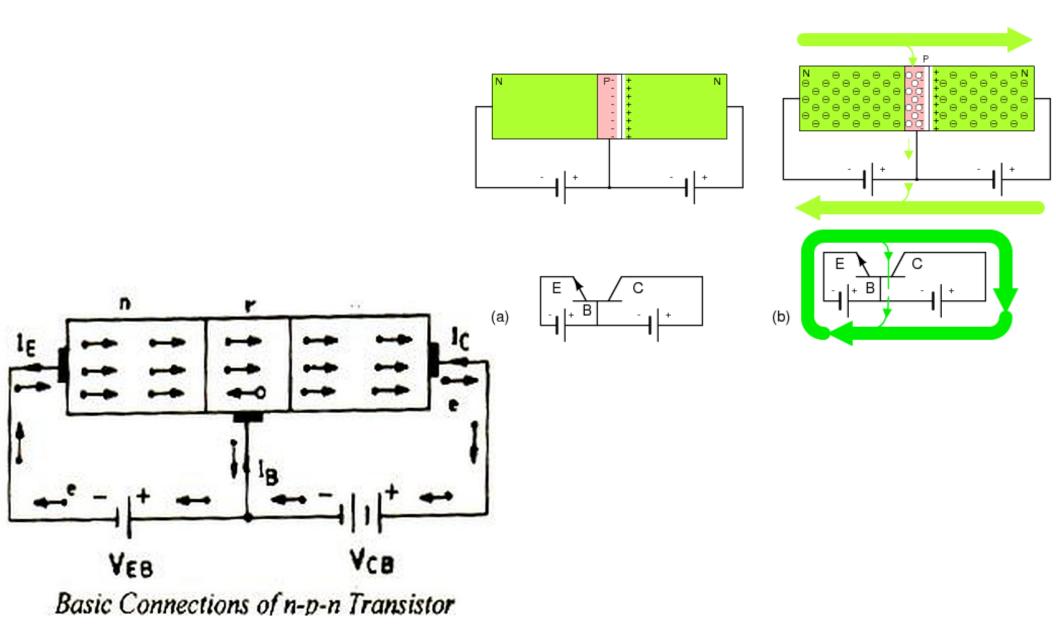

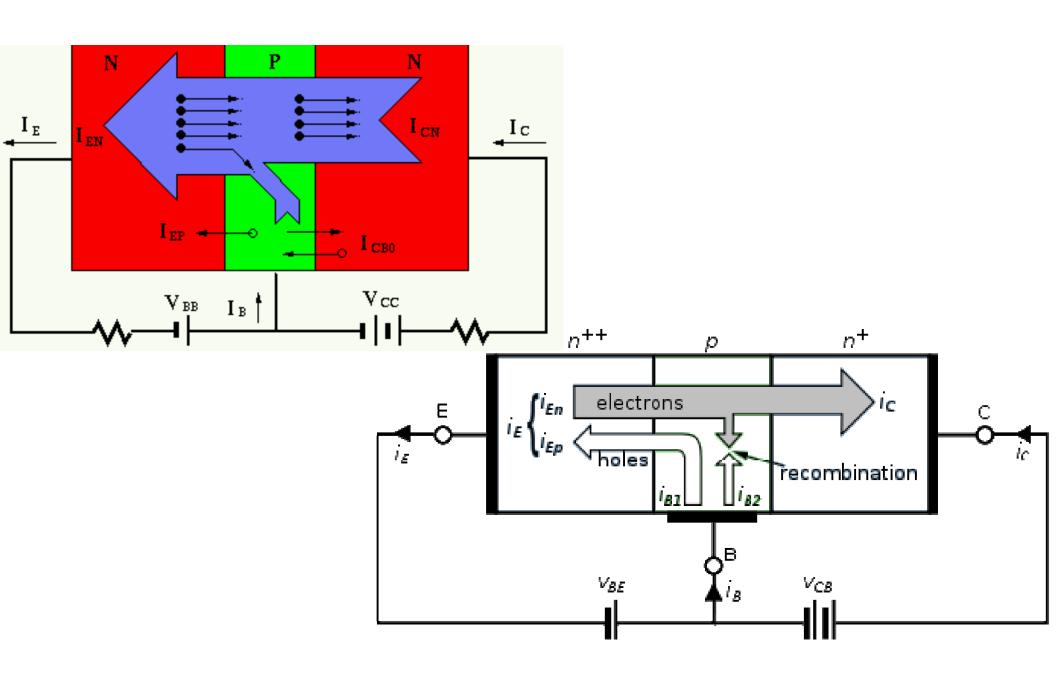

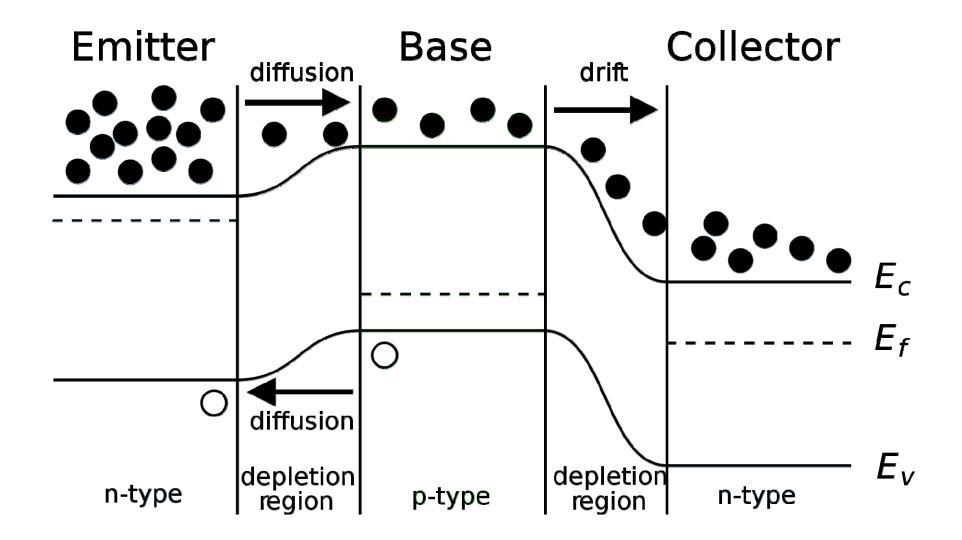

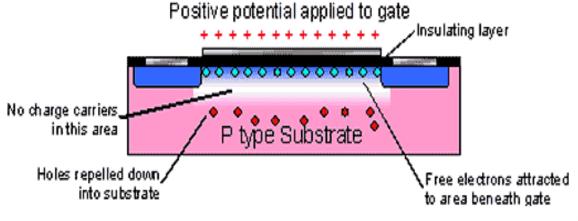

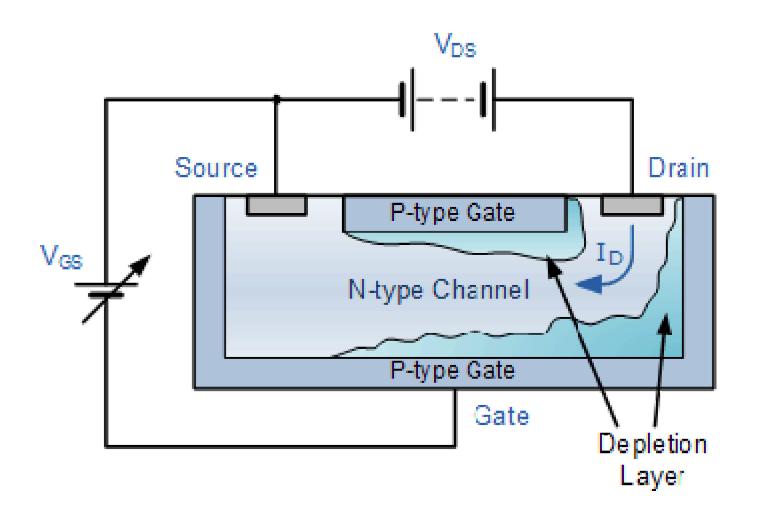

Situation after the formation of depletion region

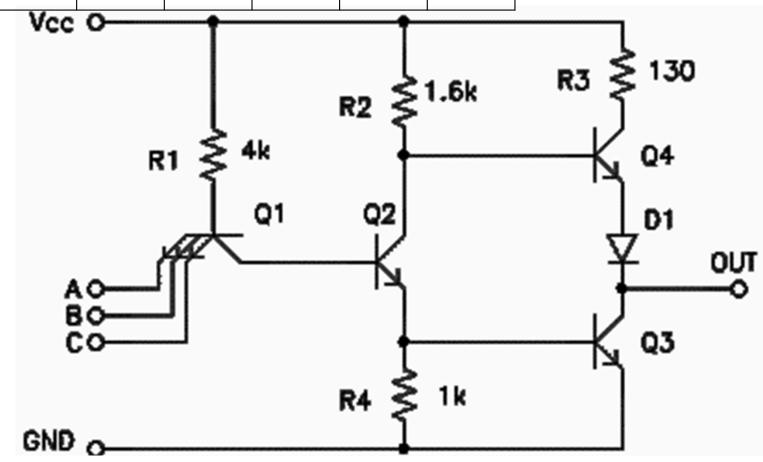

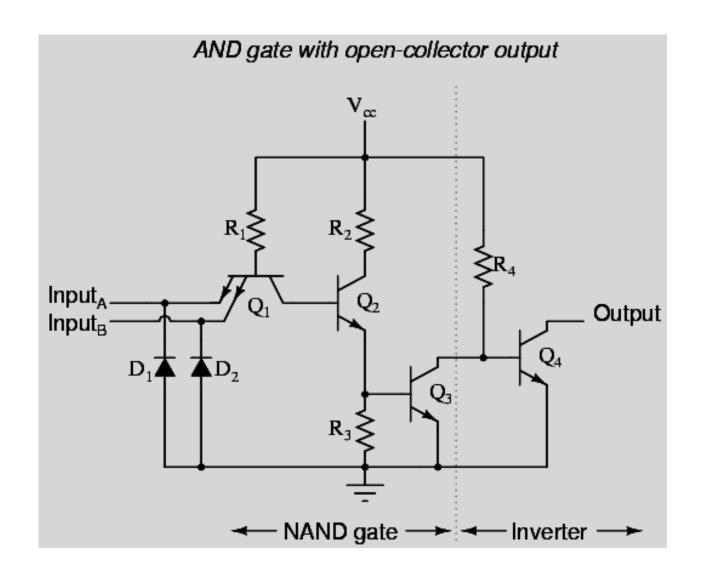

| A, B, C        | Q 1            | Q 2  | Q 3  | Q 4 | D1  | OUT  |  |

|----------------|----------------|------|------|-----|-----|------|--|

| 1, 1, 1        | Diode,<br>B->C | SATN | SATN | OFF | OFF | LOW  |  |

| Any or all "0" | ON             | OFF  | OFF  | ON  | ON  | HIGH |  |

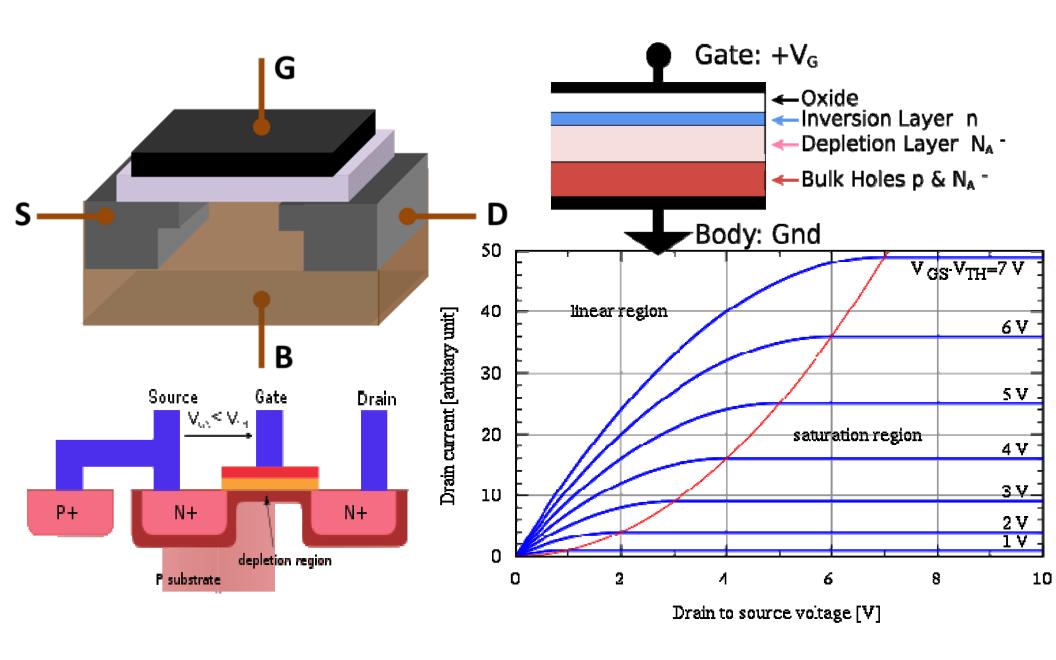

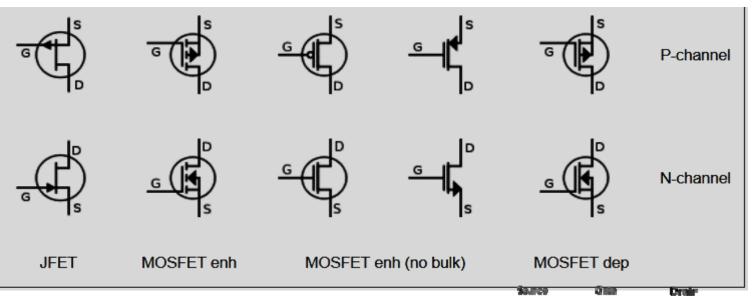

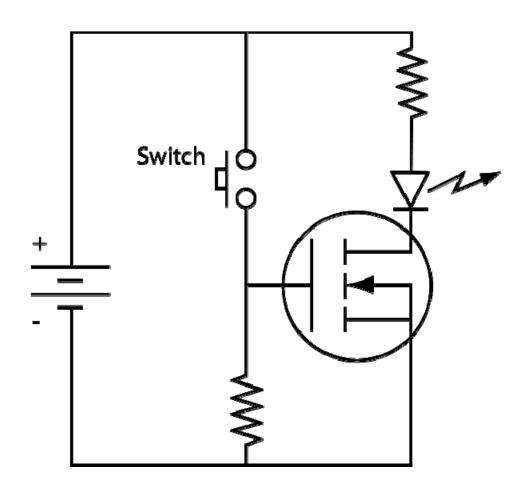

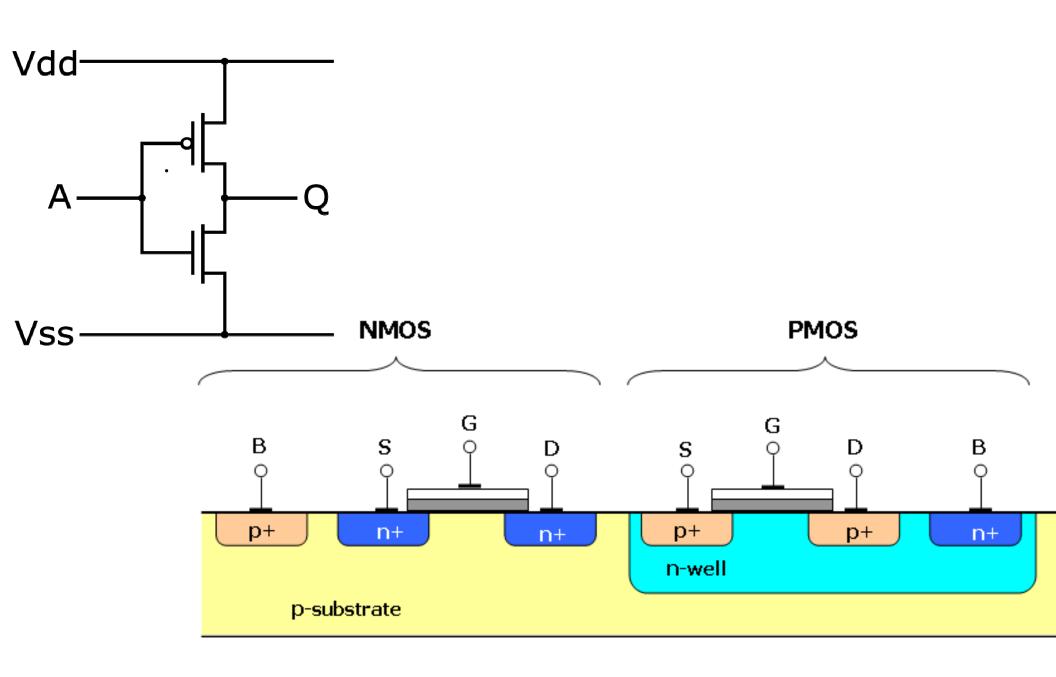

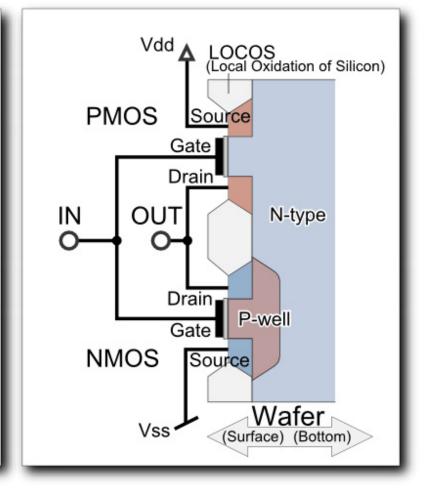

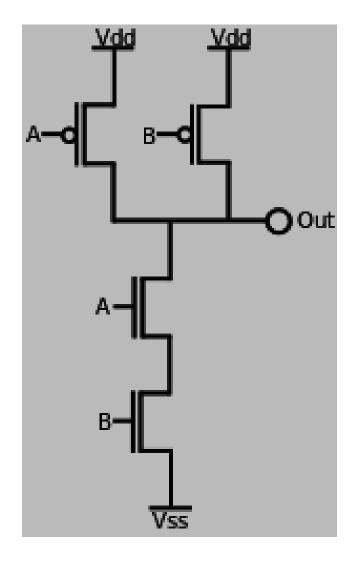

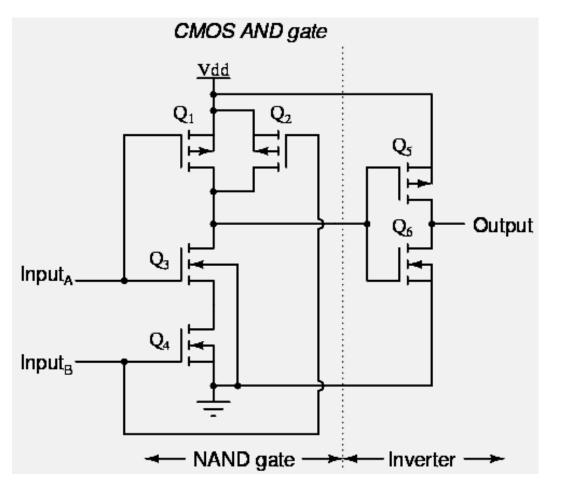

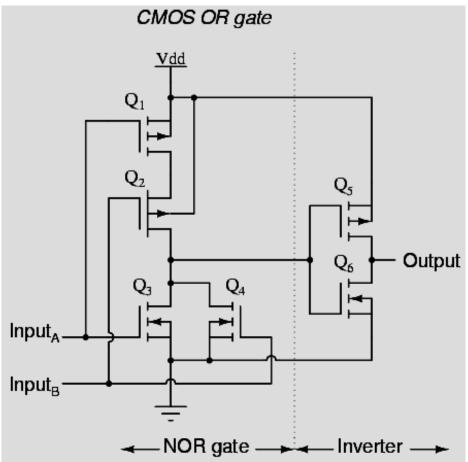

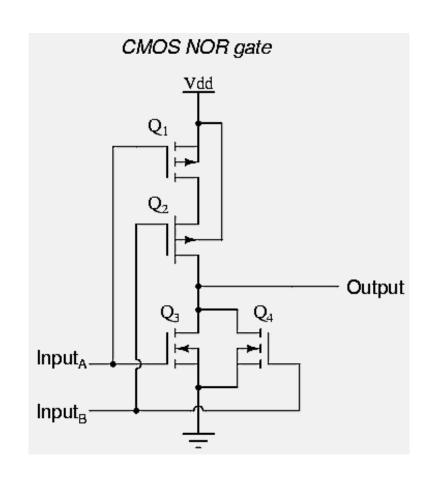

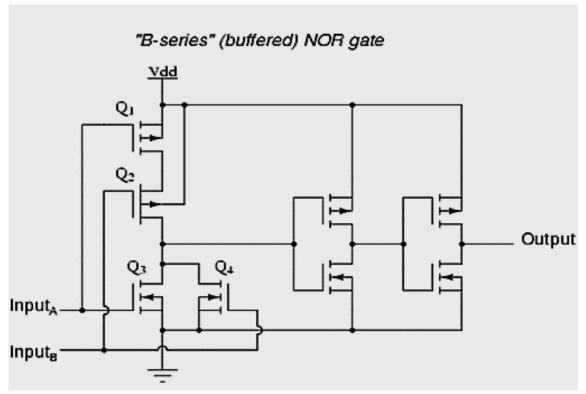

#### FET → MOSFET → CMOS

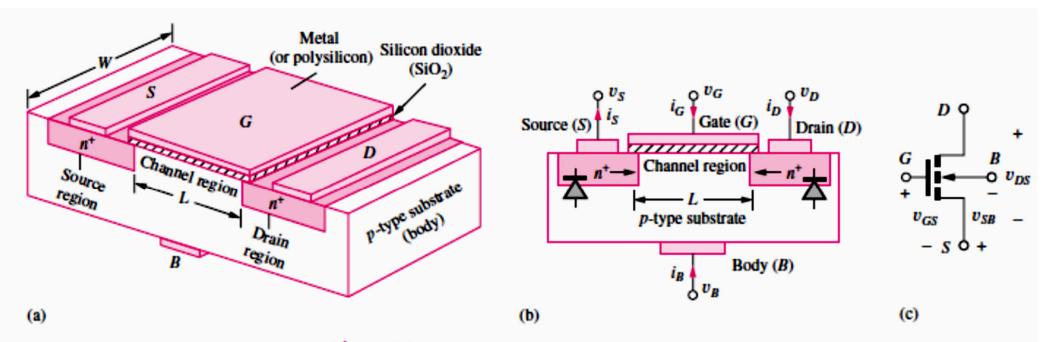

Figure 4.4 (a) NMOS transistor structure; (b) cross section; and (c) circuit symbol.

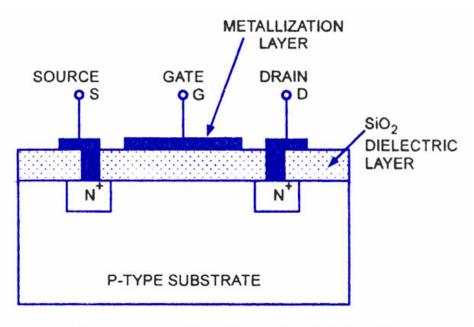

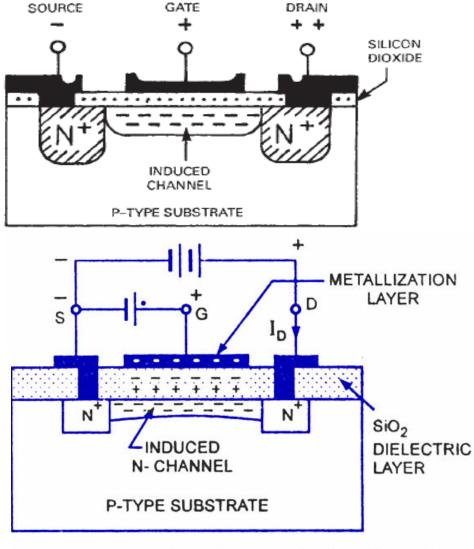

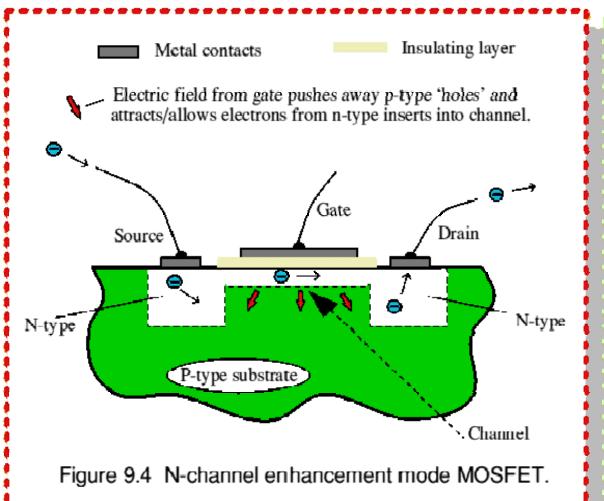

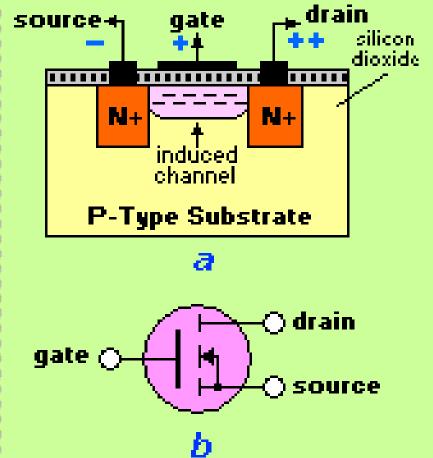

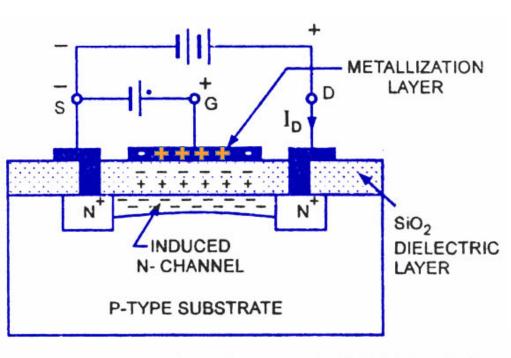

N-Channel E-MOSFET Structure

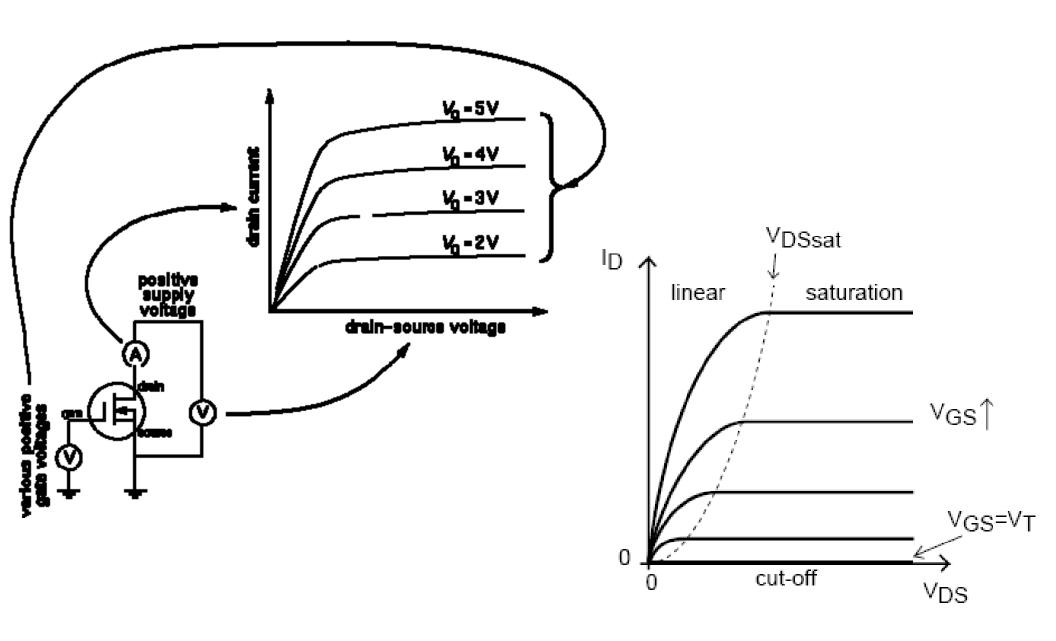

Operation of N-Channel E-MOSFET

Fig.1 – N-Channel, enhancement-mode planar MOSFET shown in section view (a), and its standard schematic symbol (b),

Operation of N-Channel E-MOSFET

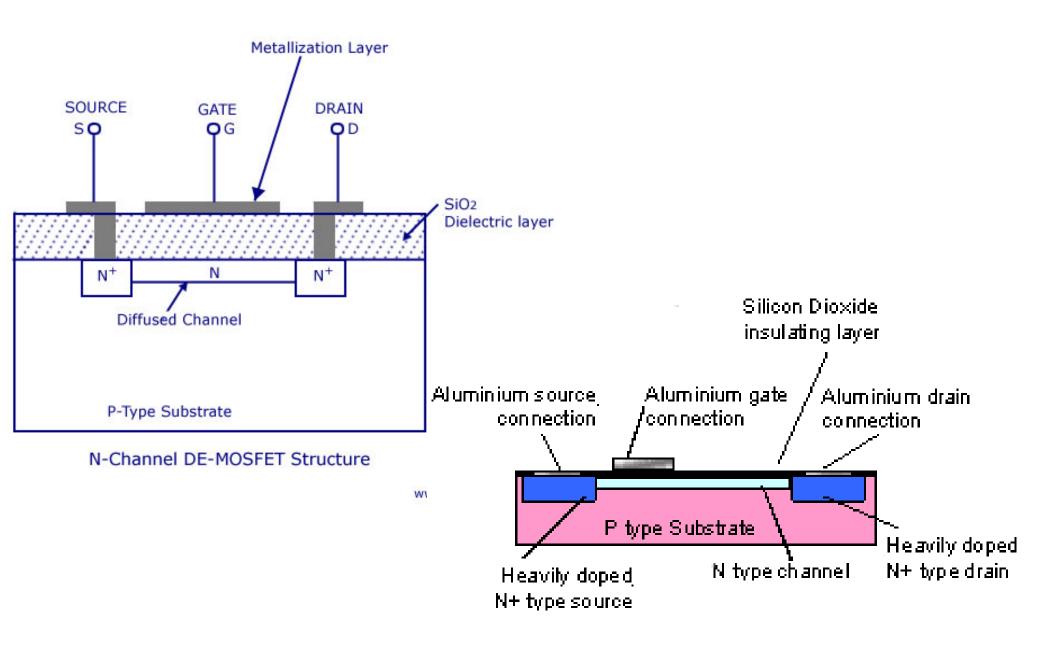

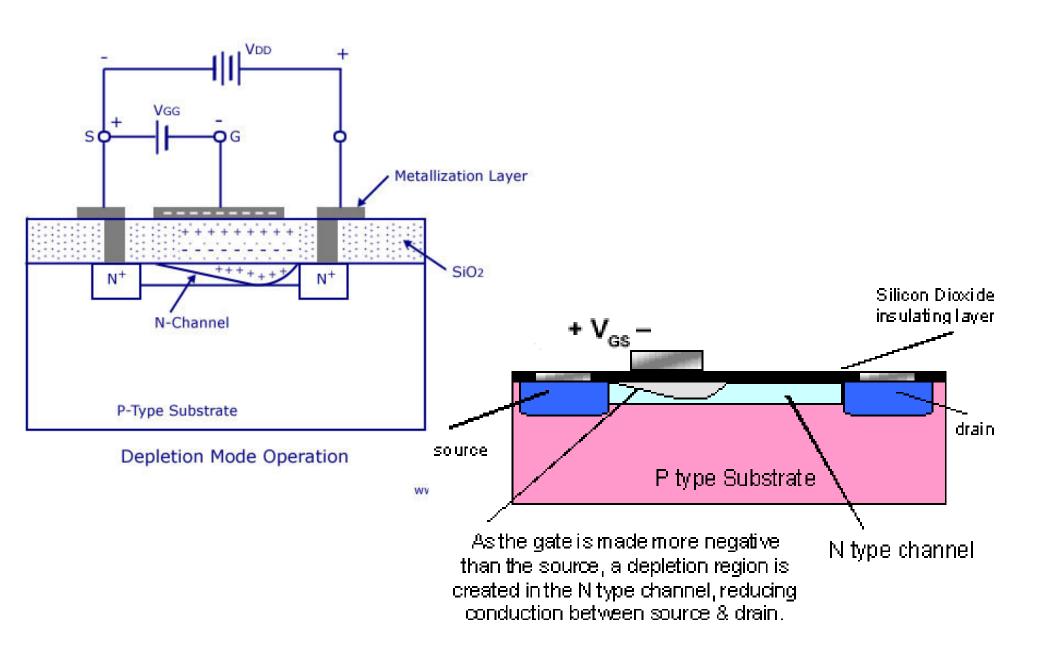

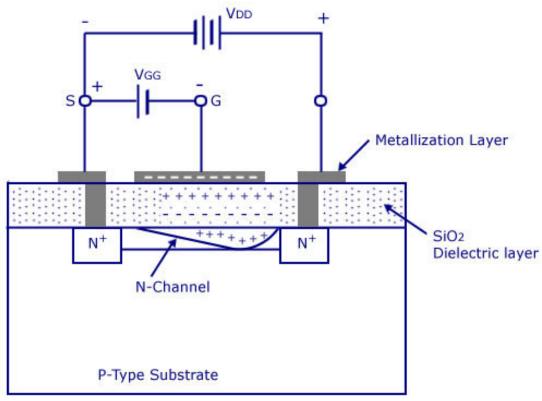

**Depletion Mode Operation**

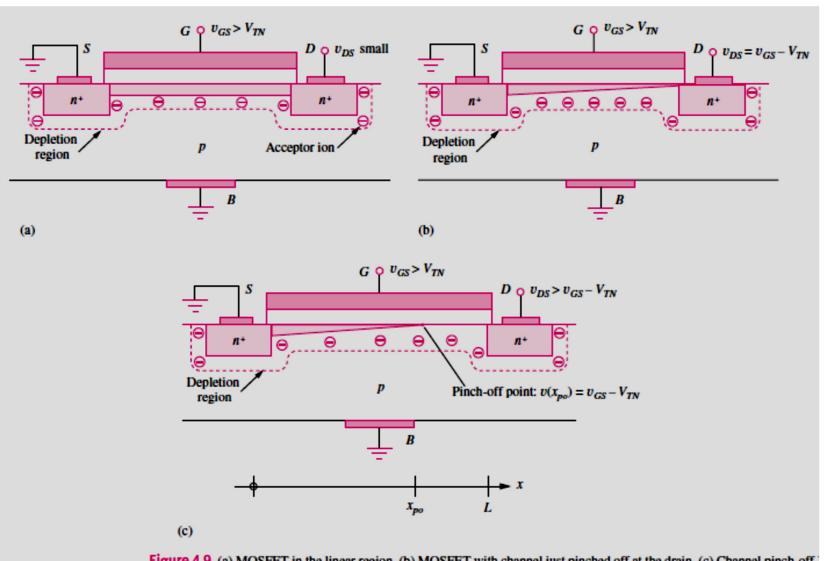

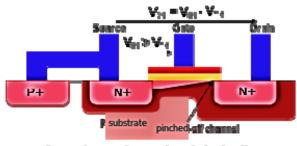

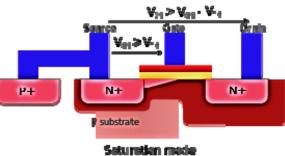

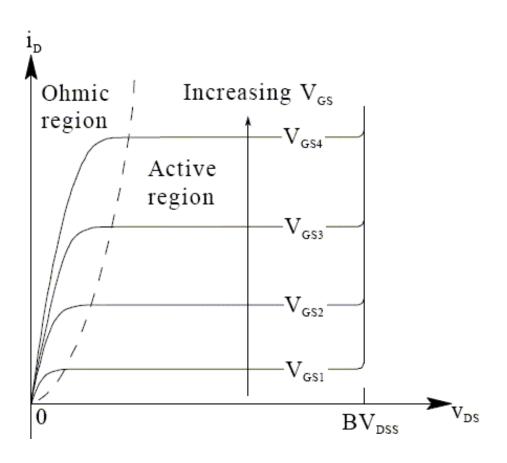

Figure 4.9 (a) MOSFET in the linear region. (b) MOSFET with channel just pinched off at the drain. (c) Channel pinch-off for  $v_{DS} > v_{CS} - V_{TN}$ .

Union operating region (whink mode):

Saturation made at point of pinch-off

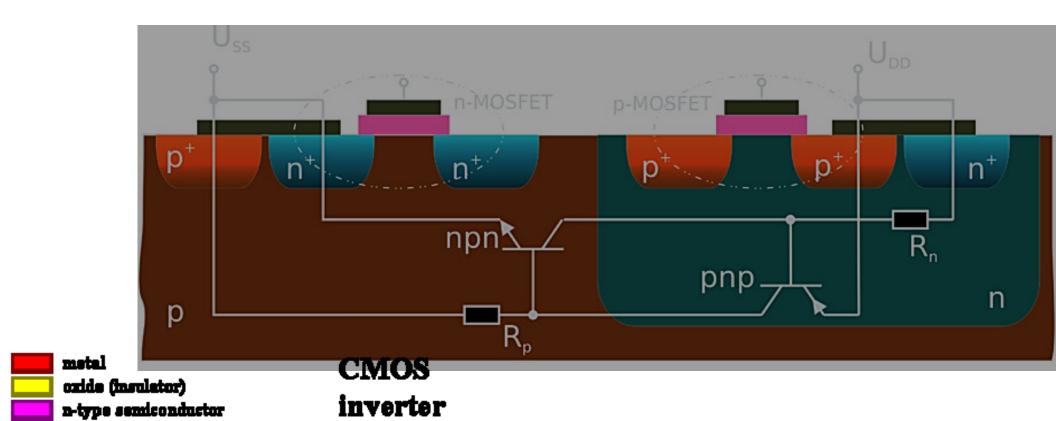

A MISFET is a metal-insulatorsemiconductor field-effect transistor.

MISFET is a more general term than MOSFET and a synonym to insulated gate field-effect transistor (IGFET).

All MOSFETs are MISFETs, but not all MISFETs are MOSFETs.

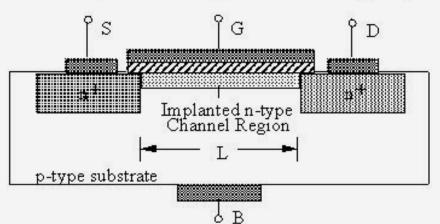

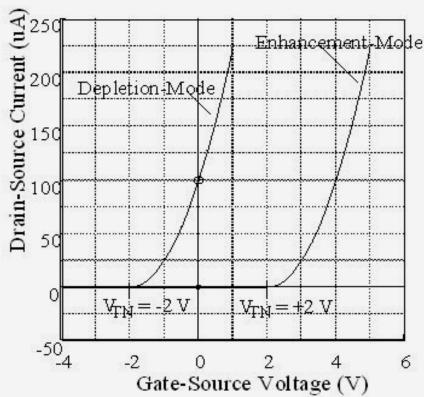

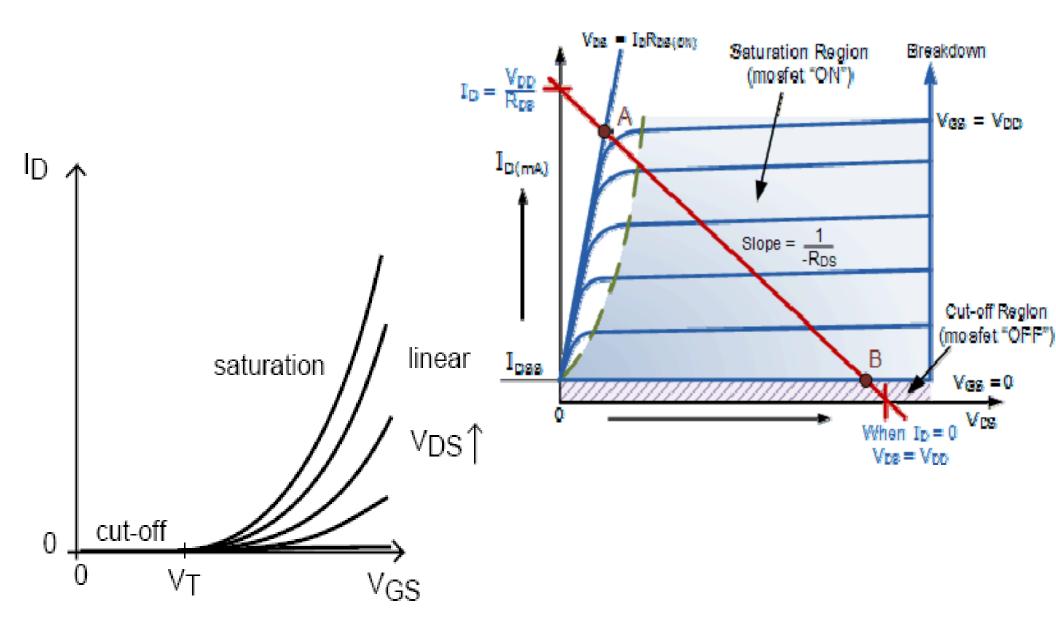

# Transfer Characteristics and Depletion Mode MOSFET

- Transfer characteristics: plot of drain current versus gate-source voltage for a fixed drain-source voltage

- If threshold voltage of NMOS transistor negative → depletion mode MOSFET (there exists an implanted n-type channel region)

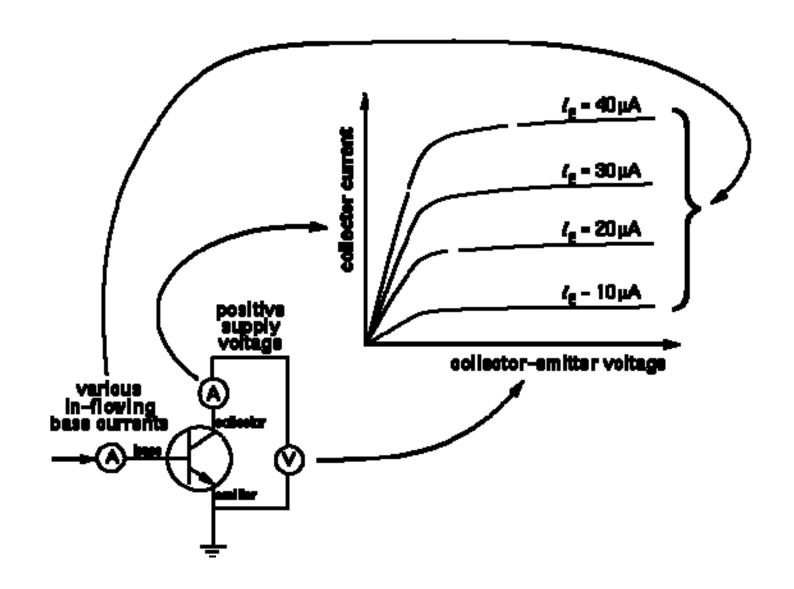

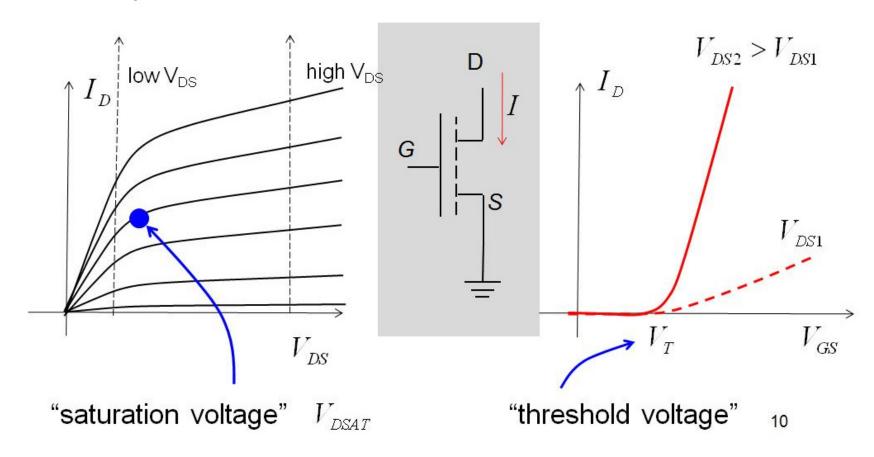

# output and transfer characteristics

## output characteristics

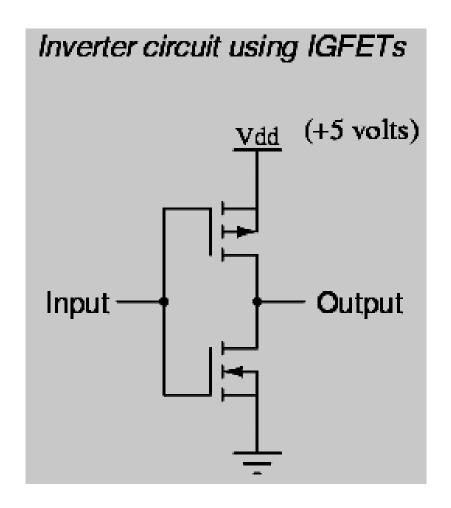

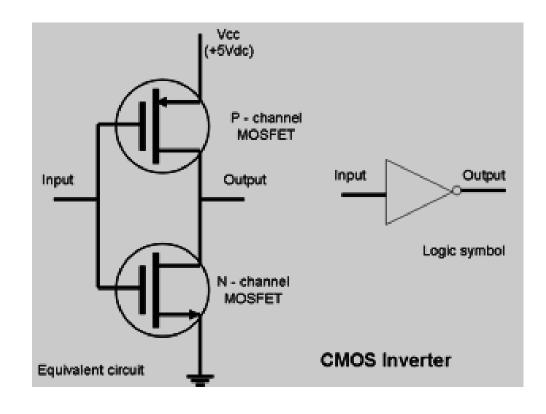

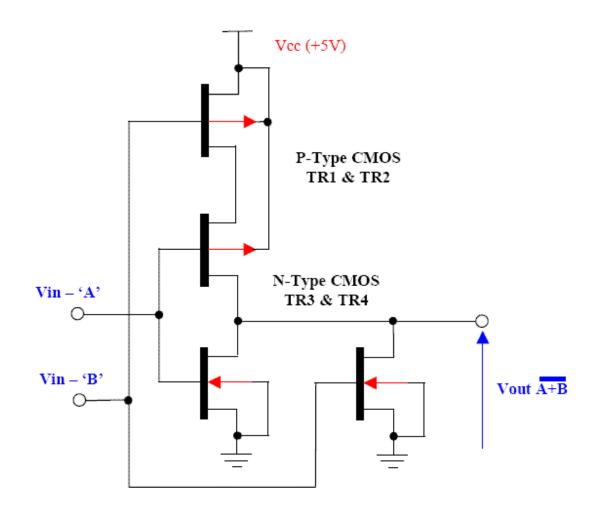

## **CMOS** inverter

#### Model chart

# Vdd **PMOS** Source Gate | Drain OUT IN Drain Gate Source **NMOS** Vss

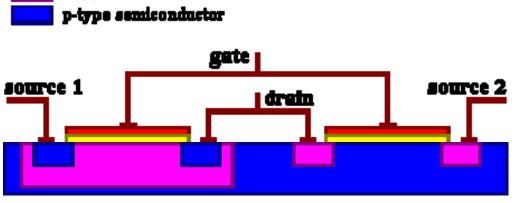

## Silicon wafer

An insulated-gate field-effect transistor or IGFET

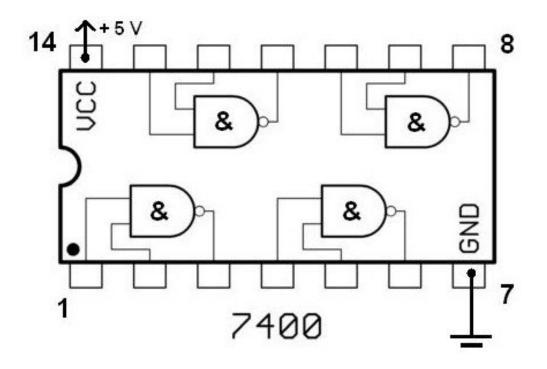

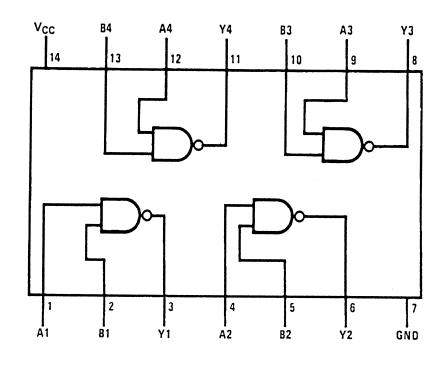

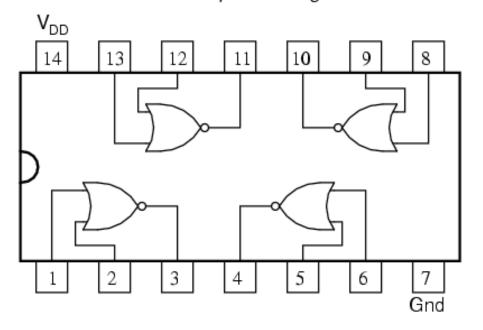

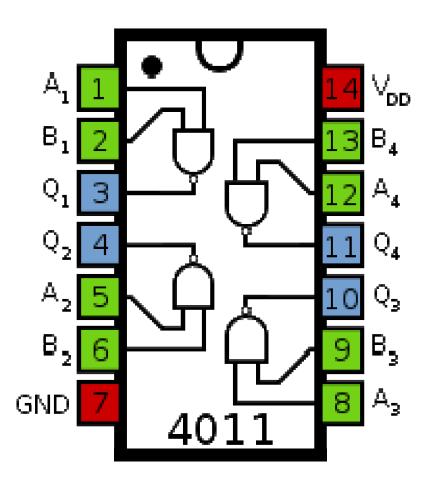

"Pinout," or "connection" diagram for the 4001 quad NOR gate

#### **To RELOOK**

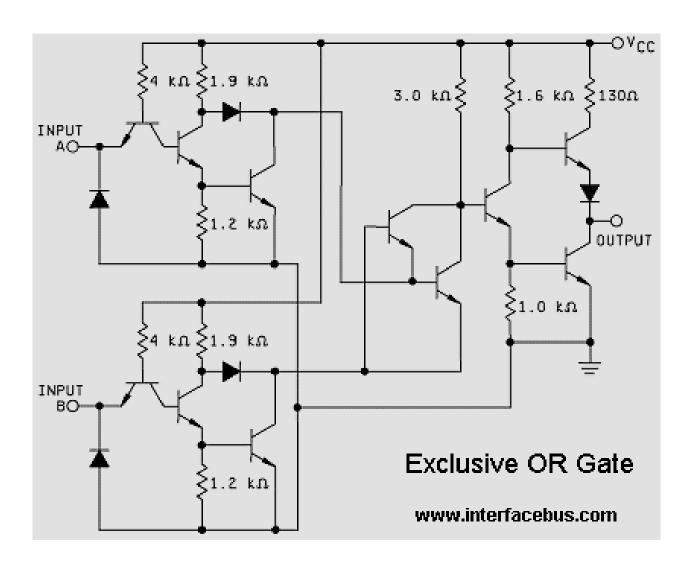

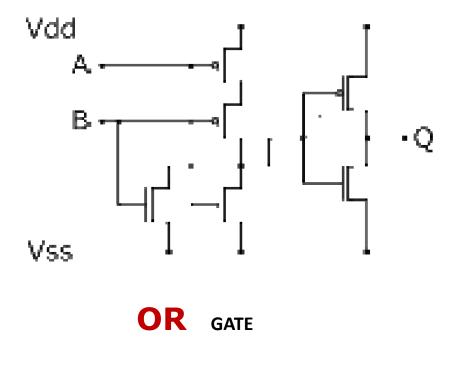

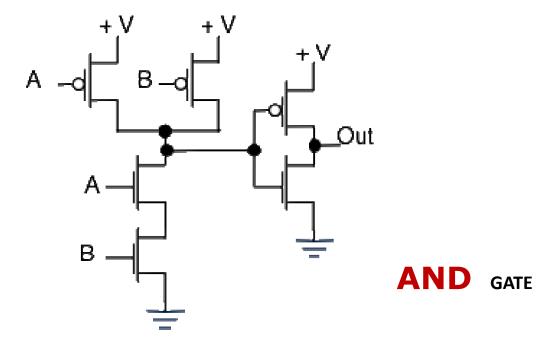

## What are these gates ??

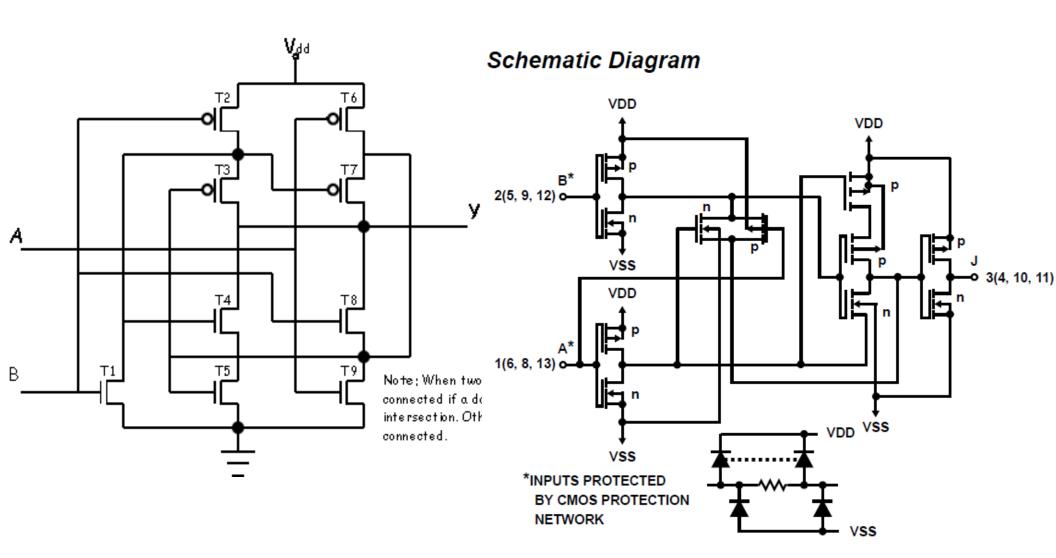

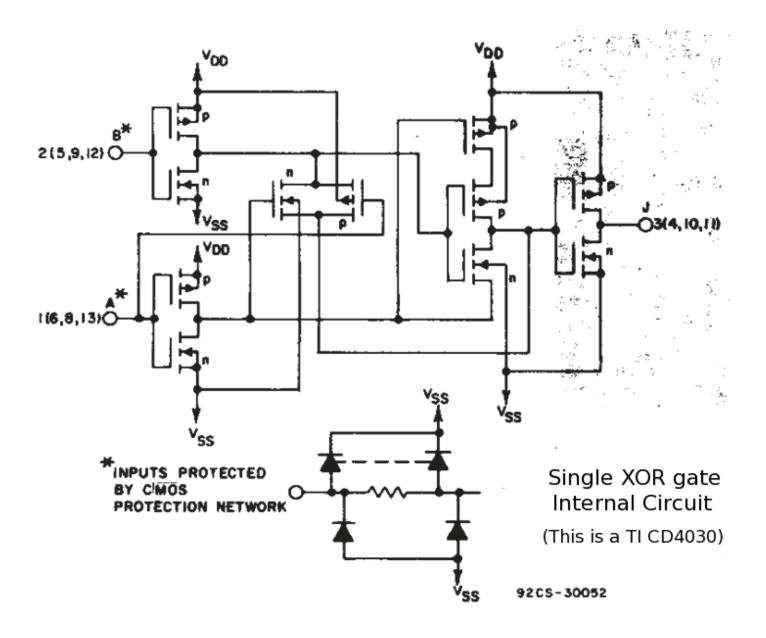

FIGURE 1. 1 OF 4 IDENTICAL GATES

#### **Dist. Laws:**

X(Y+Z) = XY + XZ;

$$X + YZ = (X+Y)(X+Z);$$

$$XY + XY' = X;$$

$$(X + Y)(X + Y') = X;$$

$$X + XY = X$$

;

$$X(X + Y) = X;$$

$$(X + Y')Y = XY;$$

$$XY' + Y = XY;$$

#### **CONSENSUS**

$$XY + X'Z + YZ = XY + X'Z$$

$$(X + Y)(X' + Z)(Y+Z) = (X + Y)(X' + Z)$$

#### **De-Morgan's Laws:**

$$(X + Y)' = X' \cdot Y'$$

$$(X.Y)' = X' + Y'$$

$$\mathsf{F} \quad \Rightarrow \quad (\mathsf{X} + \mathsf{Y}')\mathsf{Y} \quad = \quad \mathsf{X}\mathsf{Y}$$

$$F_D \rightarrow XY' + Y = X + Y;$$

$$F_C \rightarrow X'Y + Y' = X' + Y'$$