## CS2310: Digital Logic Design Lab Experiment 6

Prof. Sukhendu Das

8 September 2015

## **Problem Statement**

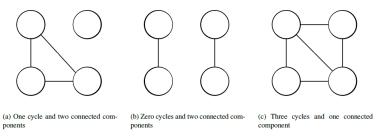

Consider a simple, undirected graph with four vertices. You will design circuits that count the following :-

- 1. The total number of cycles in the graph.

- 2. The number of connected components in the graph.

A connected component of an undirected graph is a subgraph in which any two vertices are connected to each other by paths, and which is connected to no additional vertices in the super graph.

For both problems, you will be presenting the output by displaying the corresponding number on a 7-segment display.

You are allowed to use any of the basic logic gates, adders, muxes, decoders and encoders for this assignment.

Hint: Reduce and reuse

Figure 1: Sample undirected graphs with four vertices